Vitis AI 加速 GMSL 摄像头人脸检测 - 第四部分

DPU加速器创建

本教程中使用的 Vitis 加速器构建流程采用基本平台,利用 FPGA 加速器的各种赛灵思对象 (.xo) 文件中的链接,生成最终的 FPGA 二进制文件 (.xclbin)。本教程在 DPU 上使用单个 .xo。构建 DPU 加速器请运行

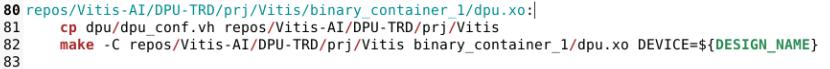

make repos/Vitis-AI/DPU-TRD/prj/Vitis/binary_container_1/dpu.xo

目标如下所示

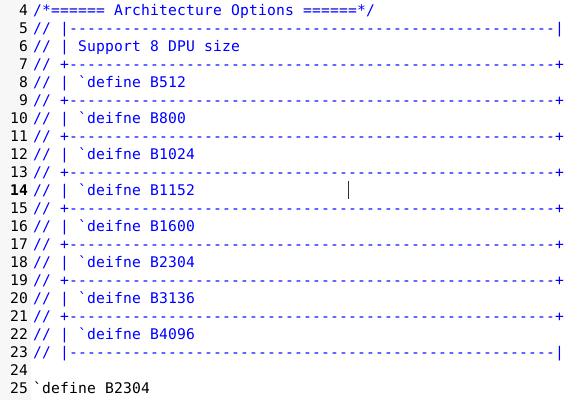

第一步是将 dpu/dpu_conf.vh 复制到构建目录中。此文件包含 DPU IP 所需的配置。该文件已存在于 Vitis-AI 存储库中,但出于演示目的,本教程构建了不同的配置。该设计具体采用了 B2304 配置,而其他一切均为默认配置。

第二步是使用 Vitis-AI 存储库中提供的生成文件构建 dpu.xo。

Vitis 平台创建

下一个构建步骤是创建 Vitis 平台。Vitis 平台包含先前构建的基础 Vivado 项目和来自 Petalinux 项目的各种组件,例如引导文件、Linux 镜像和 sysroot。要创建 Vitis 平台,请运行以下命令:

source

make vitis_platform_workspace/vitis_ai_multicam_plat/export/vitis_ai_multicam_plat/vitis_ai_multicam_plat.xpfm

目标如下所示

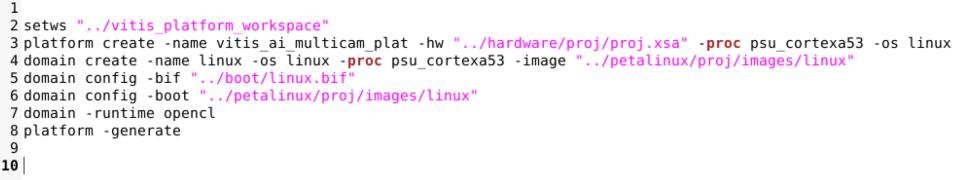

主要任务是使用赛灵思软件命令行工具 (xsct) 获取 scripts/build_vitis_platform.tcl。如下所示

该脚本执行多项 Vitis 命令。首先,基于前面步骤中的 .xsa 文件创建一个平台项目。注意,此设计使用 Petalinux 构建应用程序。如果首选在 Vitis 本身中构建应用程序,那么应该将 -sysroot 标志添加到域创建调用中,以便应用程序将针对定制的 rootfs 进行构建。然后创建一个 Linux 域,指向 petalinux 构建中的 linux 镜像。为域设置一些附加属性,然后生成平台以创建 .xpfm 文件。

将 dpu.xo 文件与基本平台链接,以创建最终的 FPGA 二进制文件 (.xclbin),使用以下命令

make repos/Vitis-AI/DPU-TRD/prj/Vitis/binary_container_1/dpu.xclbin

调用 Vitis v++,如下所示

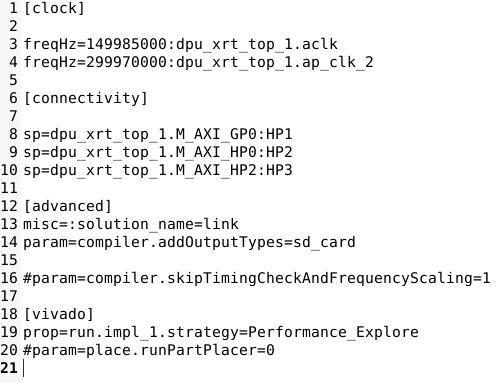

该步骤将 dpu/prj_config 文件作为输入,通知 Vitis 如何将 DPU 加速器连接到平台的其余部分

时钟的 freqHz 属性与时钟向导的实际输出频率相匹配。根据块设计中的 sptag 属性进行连接。

模型编译

下一步是构建神经网络自身的模型。这涉及到(在工具 docker 容器内)调用Vitis-AI dlet 命令来生成 DPU 配置文件 (DCF),然后为本教程中使用的特定模型(密集盒)生成 DPU 可执行文件。利用以下命令来构建

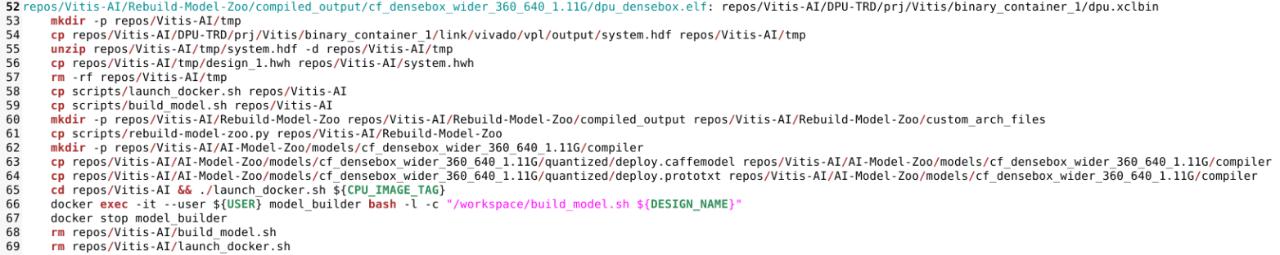

make repos/Vitis-AI/Rebuild-Model-Zoo/compiled_output/cf_densebox_wider_360_640_1.11G/dpu_densebox.elf

由于现有的 Vitis-AI 库组织方式,该 make 目标准备文件结构以便于调用 docker 容器内的事物的方式较为繁杂

第一个任务是从 Vivado 项目中的 system.hdf 中提取 hwh 文件。Vitis AI 工具使用此文件来解析有关 DPU 配置的各种信息。该文件是创建 DCF 的 DLet Vitis-AI 工具的输入项。

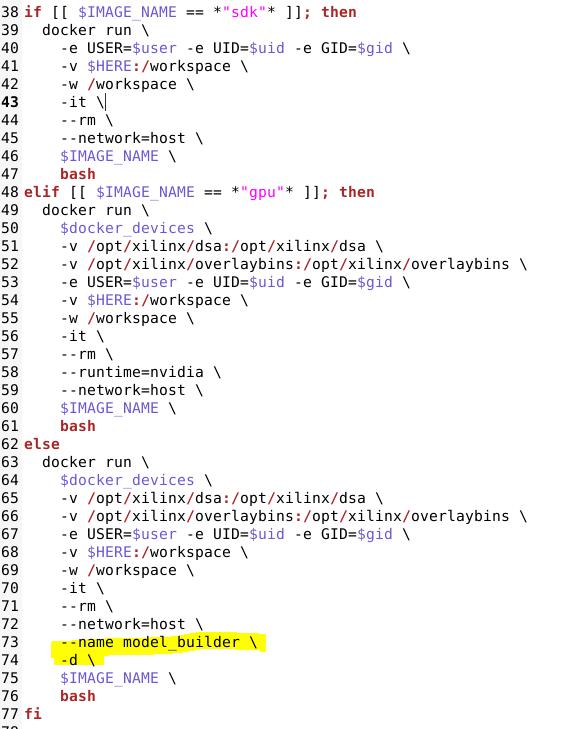

接下来,将 scripts/launch_docker.sh 复制到 Vitis-AI 库中。该文件类似于 Vitis-AI 库附带的 repos/Vitis-AI/docker_run.sh,只是稍微修改为

- 添加 -d switch 在后台运行 docker 容器

- 添加 --name model_builder 开关,以便过后能够与其连接并在 docker 容器内执行命令

scripts/build_model.sh 也被复制到 Vitis-AI 库中。这个脚本实际上是在 docker 容器中执行的

该脚本首先设置 Vitis-AI 工具环境,调用 dlet,然后运行 scripts/rebuild-model-zoo.py。build-model-zoo.py 调用 vai_c_caffe 生成 DPU 可执行文件。

现在目录结构已确认正确,将执行 launch_docker.sh 来启动 docker 容器。然后在该容器中执行 build model.sh。最后,停止 docker 容器,并清理外来文件。

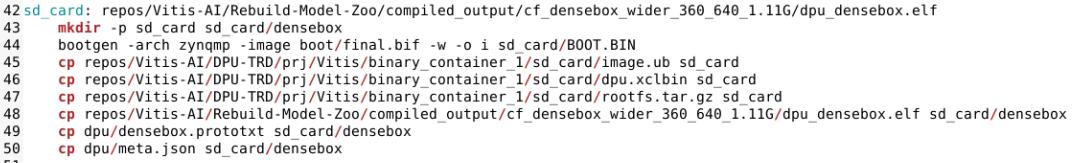

SD卡镜像

生成文件的最后一步是将所有必要的二进制文件复制到 sd_card 目录。

make sd_card

Bootgen 也在这个步骤中调用来创建最终的 BOOT.BIN,其中包含由Vitis v++创建的比特流。

演示

要运行演示,请遵循“快速入门”章节中从“准备SD卡”开始的步骤。

小结

本教程展示了构建加速实时摄像头流上实时神经网络处理的自定义 Vitis AI 平台所需的所有步骤。从 FPGA 平台设计开始,展示了启用 DPU 加速器的特殊注意事项。而后对软件设计做出阐释,以强调在 Linux 中启用 DPU 接口所需的步骤。 最后,Vitis 平台开发,并与 Vitis AI 的 DPU 可执行输出集成以完成设计。完成本教程后,系统设计人员将具备利用 Xilinx 独特的机器学习加速技术在定制设计中进行部署所需的所有技能。