使用 Vitis 设计基于收发器的应用

硬件工程师如何从 Vitis 中获益?

赛灵思 Vitis™ 统一软件平台支持在各类赛灵思平台(包括 FPGA、SoC 和Versal ACAP)上开发嵌入式软件和加速应用。

对于收发器应用,硬件设计师通常采用 Vivado 中的 RTL 和 IPI 设计方法。本文研究了如何采用 Vitis 技术创建基于 GT 的 IP 设计。

在 Vitis 软件平台上,可以生成基于 GT 的 IP shell 设计,并且还提供了内核服务,用户可以通过该服务使用简单的 C 代码生成/移植定制模式。其他基于 GT 的 IP 功能也可以移植到基于 Vitis 的系统中。

Vitis 技术为软硬件工程在设计和验证流程中的协作提供了统一的方法:Emulate-HW、Emulate-SW 以及系统构建和测试。

设计理念与架构

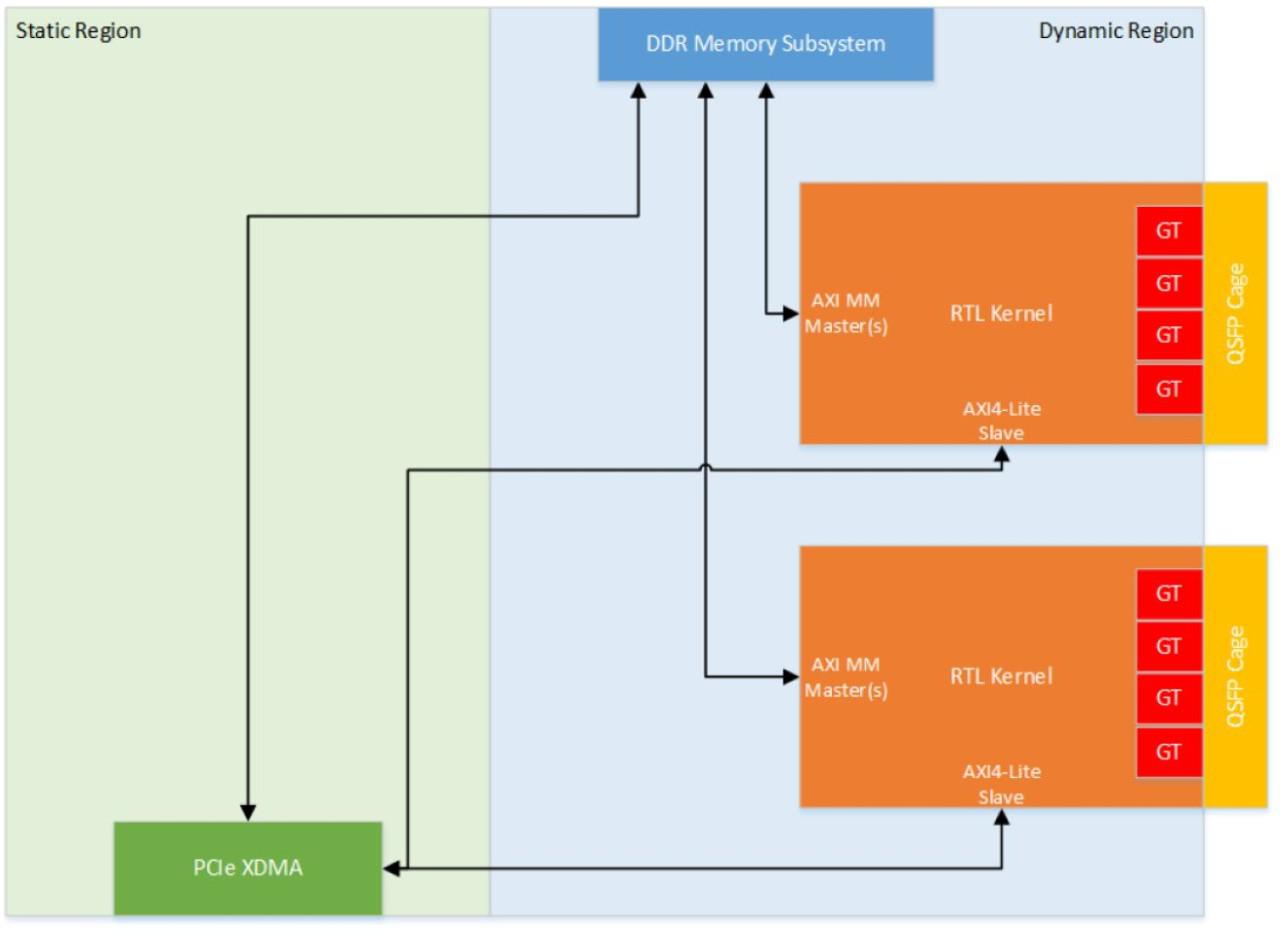

下面是一个基于 Alveo U200 数据中心加速器卡的内核示例。本 shell 示例演示了两个 RTL 内核(动态区域)。动态区域的大小取决于所使用的 PL 资源,包括 LUT、DSP、IO 和存储器。AXI 接口部署用于 RTL 内核、本地存储器子系统和主机存储器之间的数据传输。静态区域依赖于平台,并提供到主机系统和主机存储器的网关。

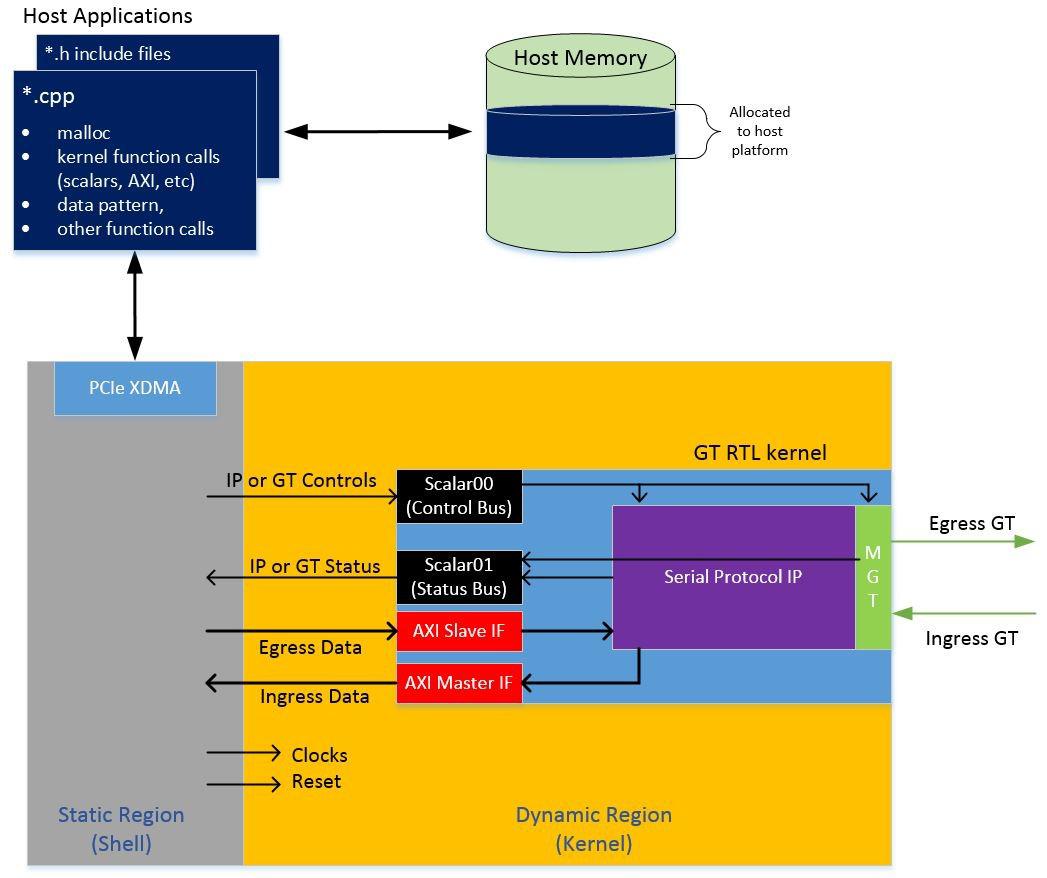

在上述 U200 XDMA Alveo 平台的基础上,提出了一种简单的 GT 内核平台架构:

- 静态区域 (shell):在平台中提供,它包括

- PCIe XDMA 接口

- AXI 主接口

- 动态区域(内核)

- 一个带有 AXI Streaming接口的串行协议 IP(如 Aurora 或GT 向导)

- 一个 64 位 AXI 主接口,用于传输通过收发器传入的入口数据

- 一个 64 位 AXI 从接口,用于在主机应用中传输用户创建的出口数据(如 C++ 代码)

- 一个 64 位 scalar00,供用户应用控制(如 GT 回送)内核

- 一个 32 位 scalar01,供内核向用户应用发回报告(例如链接)

为了简化设计,平台上采用了两个64位AXI Streaming 接口进行数据传输。如果需要本地存储器,Alveo U200 卡上的 DDR 存储器可以与存储器映射 AXI 接口和内核中的存储器控制器一起使用。

在内核中添加标量寄存器以方便对收发器进行直接访问。Scalar00 是用于驱动收发器输入的 64 位控制寄存器。Scalar01 是由收发器输出驱动的 32 位状态寄存器。未使用的位被保留,如果需要,可用于串行协议 IP 中的附加控制/状态信号。

Scalar00 |

Scalar01 |

|||

Bit |

Control |

Bit |

Status |

|

0 |

QPLL0RESET |

0 |

QPLL0LOCK |

|

1 |

QPLL1RESET |

1 |

QPLL1LOCK |

|

2 |

CPLLRESET |

2 |

CPLLLOCK |

|

3 |

GTTXRESET |

3 |

GTPOWERGOOD |

|

4 |

TXPMARESET |

4 |

TXRESETDONE |

|

5 |

TXPCSRESET |

5 |

TXPMARESETDONE |

|

6 |

GTRXRESET |

6 |

RXRESETDONE |

|

7 |

RXPMARESET |

7 |

RXPMARESETDONE |

|

8 |

RXPCSRESET |

8 |

RXCDRLOCK |

|

9 |

RXCDRRESET |

9 |

RXPRBSERR |

|

10 |

RXBUFRESET |

31:10 |

RESERVED |

|

13:11 |

GT_ LOOPBACK |

|||

18:14 |

TXDIFFCTRL |

|||

23:19 |

TXPRECURSOR |

|||

28:24 |

TXPOSTCURSOR |

|||

25 |

TXELECIDLE |

|||

26 |

TXINHIBIT |

|||

27 |

TXPOLARITY |

|||

28 |

RXPOLARITY |

|||

29 |

RXLPMEN |

|||

30 |

RXCDRHOLD |

|||

34:31 |

TXPRBSSEL |

|||

38:35 |

RXPRBSSEL |

|||

63:39 |

RESERVED |

|||

Vitis 设计流程

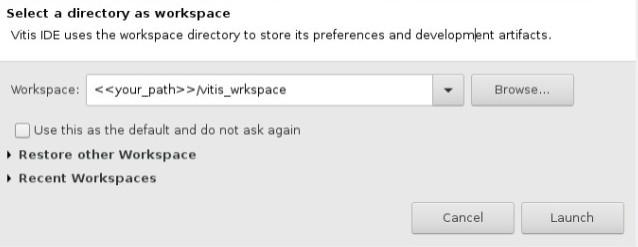

赛灵思的新平台 Vitis(来自 Vivado 2019.2 版及更高版本)用于构建主机应用。以下说明基于带有 Alveo U200 XDMA 平台的 Linux RedHat 服务器。

为 Vivado 2019.2 版(或更高版本)设置源,并在 Linux 命令提示符中调用 Vitis 技术

创建您的工作区,然后单击“Launch”

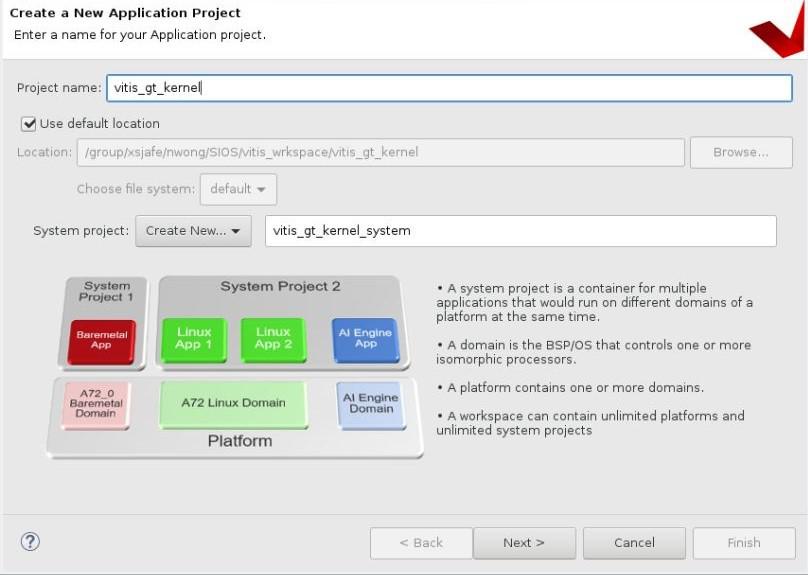

在 Welcome 页中选择“Create Application Project”

命名新的应用项目(例如 vitis_gt_kernel),然后单击“Next”

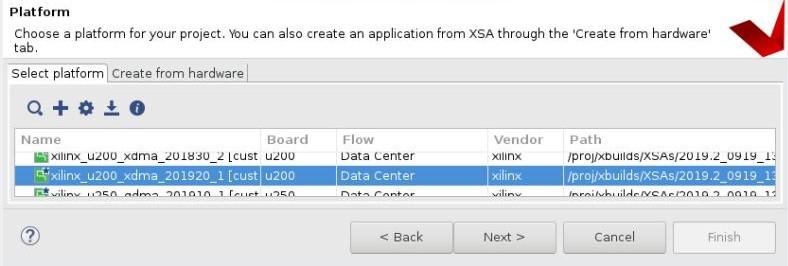

为项目选择一个平台,然后单击“Next”

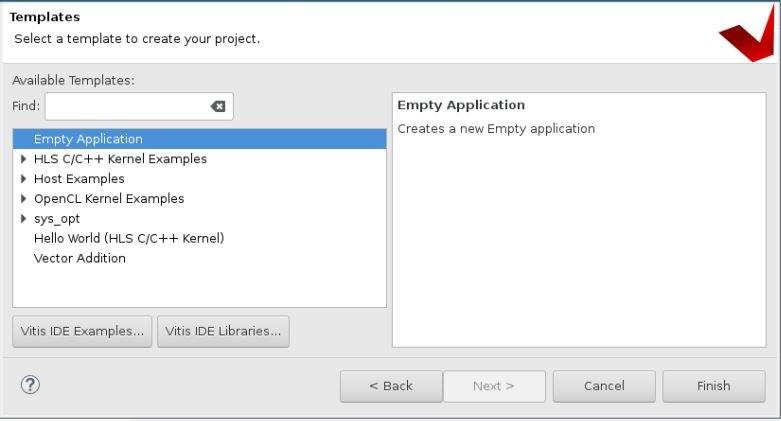

选择模板创建项目(空白应用),然后单击“Finish”

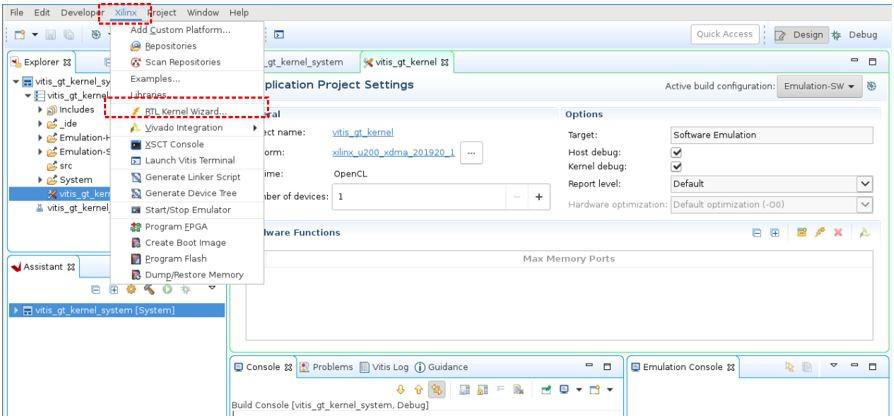

当 Vitis 工作区 GUI 出现后,选择“Xilinx”选项卡,然后单击“RTL Kernel Wizard”

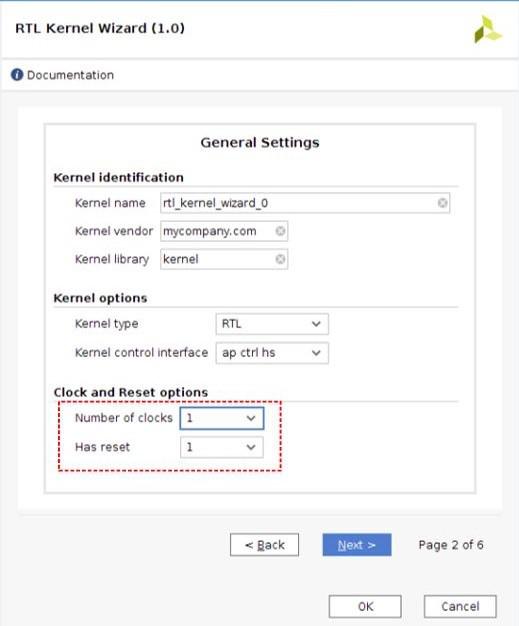

随后将出现 RTL 内核向导 GUI(可能需要一分钟以上,具体取决于您的系统)并且有 6 个向导页

- 第 1 页:欢迎页,然后单击“Next”

- 第 2 页:常规设置,选择所需的时钟数和重置数,然后单击“Next”

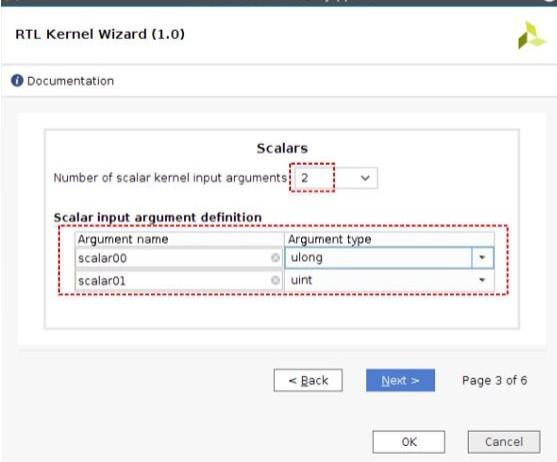

- 第 3 页:设置标量定义,然后单击“Next”

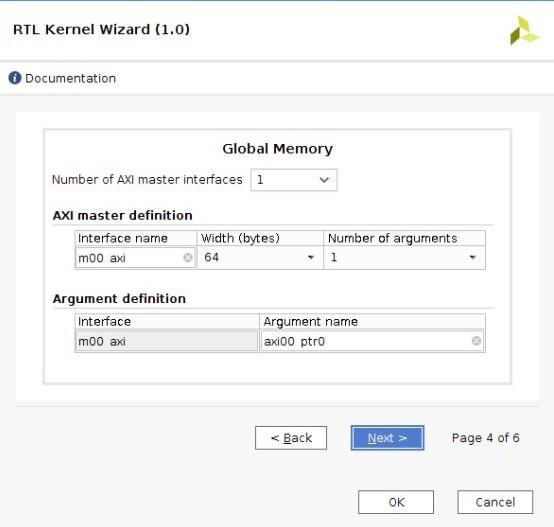

- 第 4 页:选择 AXI 主接口的数量和名称(这针对的是 shell 中的全局存储器),然后单击“Next”

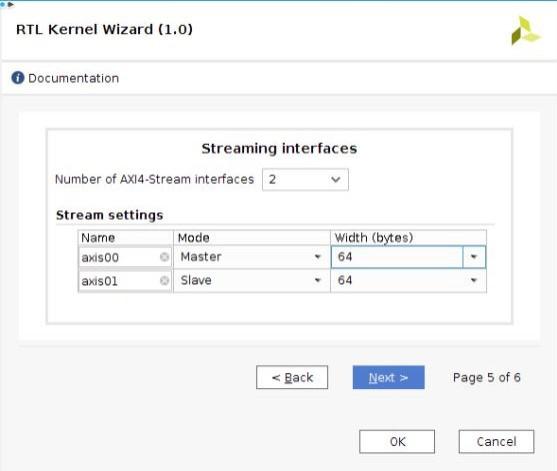

- 第 5 页:选择 AXI4-Streaming 流接口(本示例针对一个主接口和一个从接口),然后单击“Next”

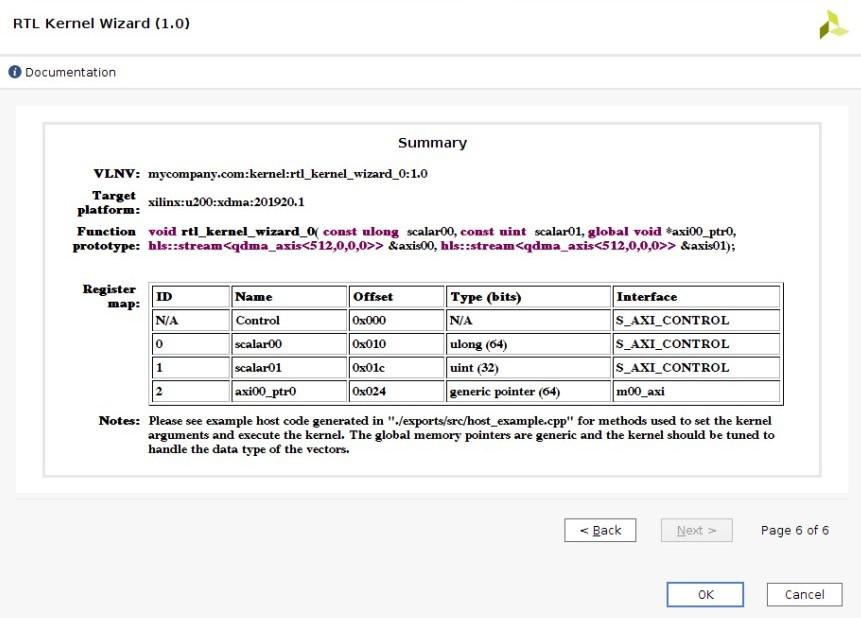

- 第 6 页:这是摘要页,它显示了该内核的函数原型,此函数将被纳入 Vitis 环境,并且可以用于主机应用编码使用(请注意,由于没有映射到主机存储器,所以寄存器映射表中没有显示 2 个 AXI4-Streaming 流接口),然后单击“OK”

- Vitis 将完成 RTL 内核向导并启动 Vivado。这可能需要超过一分钟的时间

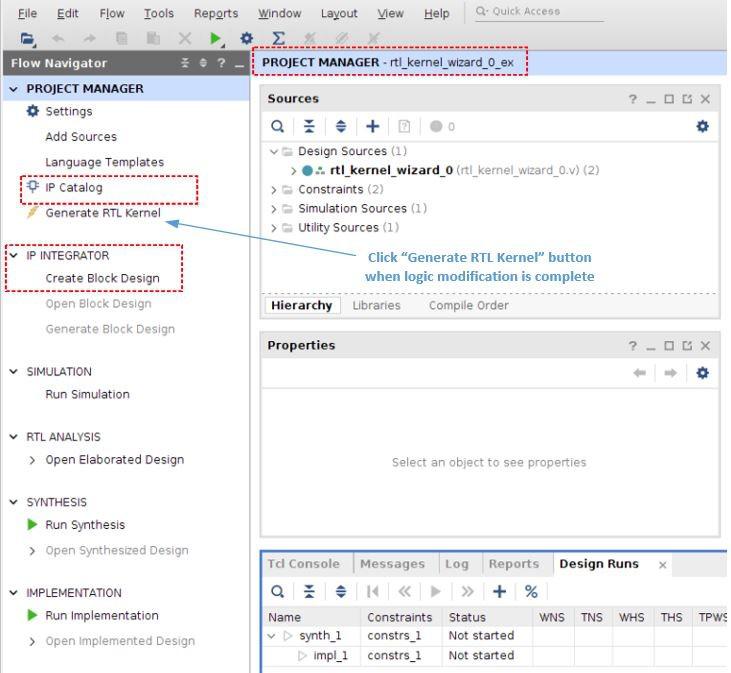

对于创建了内核向导的 Vivado 项目,您可以使用 IP 目录(RTL 设计流程)或 IP 集成器(IPI 设计流程)添加串行协议 IP 和定制逻辑

选择所需的封装选项,然后单击“OK”。生成完成后,单击“Yes”退出 Vivado。在 Vitis RTL 内核导入信息弹出窗口中单击“OK”

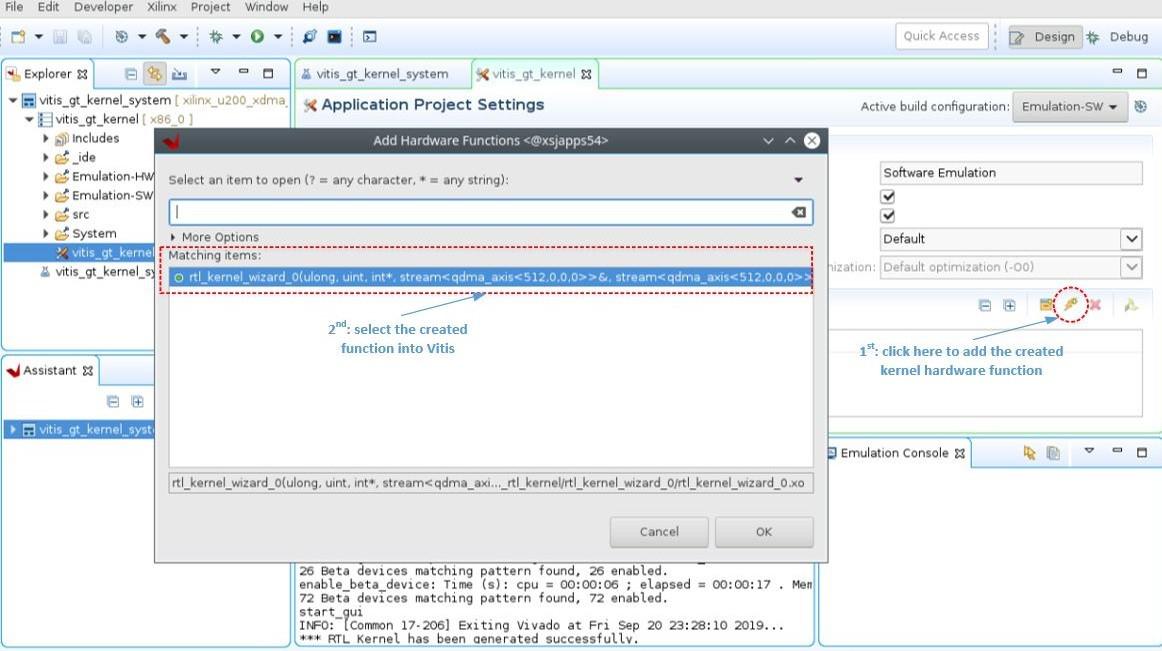

返回 Vitis 项目 GUI 后,添加创建的硬件功能,然后单击“OK”

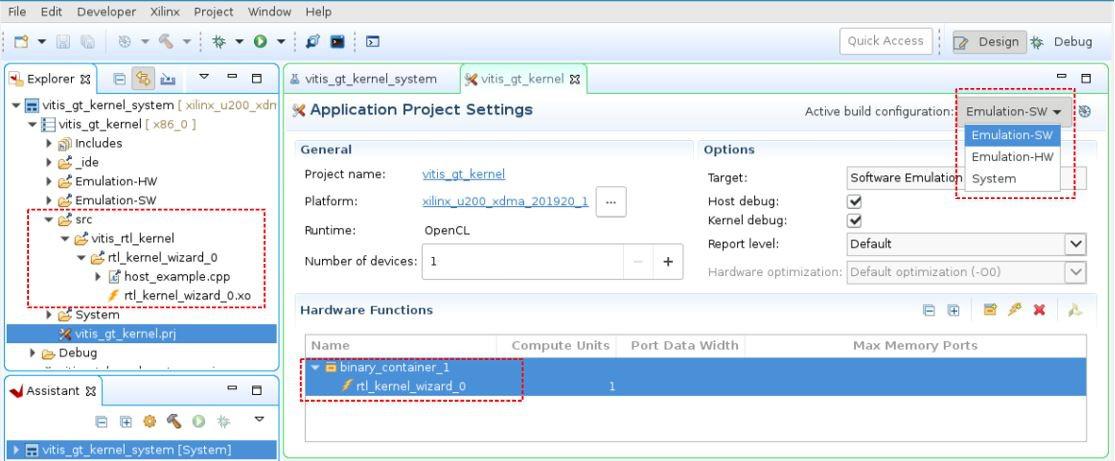

现在导入了内核设计(如 src 文件夹所示)。您可以选择 3 个激活的生成配置选项中的其中一个选项:

- Emulate-HW: 硬件仿真

- Emulate-SW: 软件仿真(比模拟硬件更快)

- 系统:构建硬件

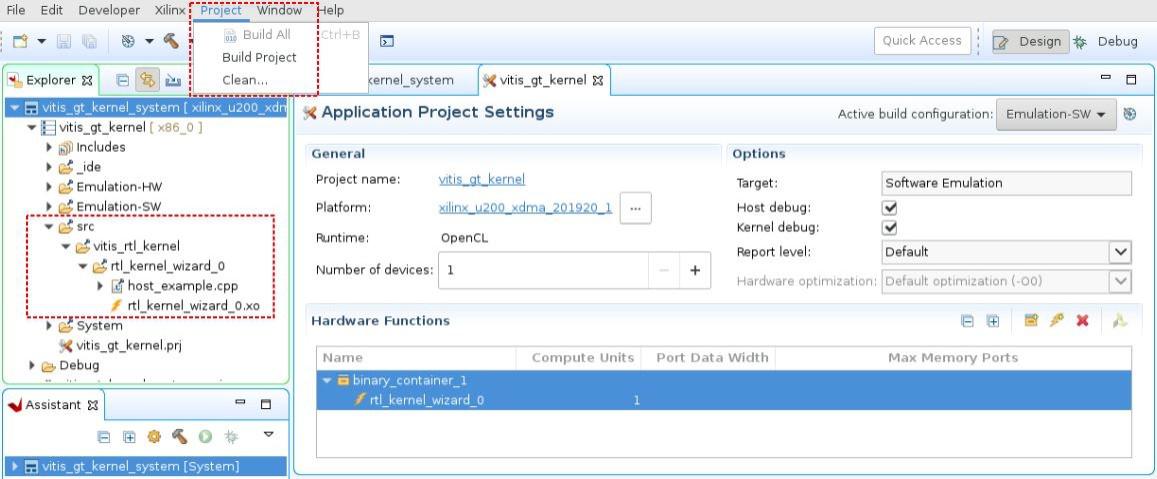

单击“Project”选项卡,然后单击“Build Project”生成所需的配置

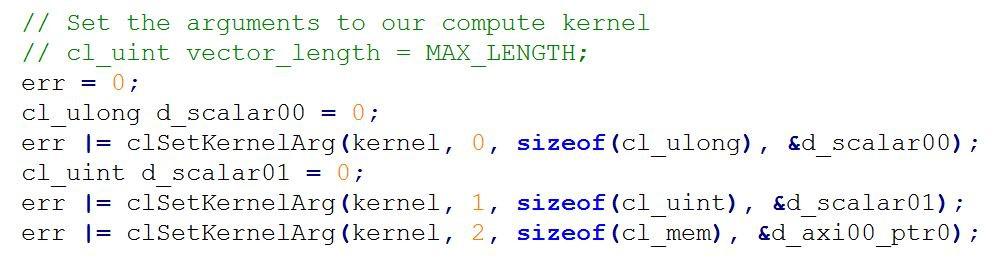

上图显示 Vitis 生成host_example.cpp(主机应用代码),用户可以通过修改来定制其测试流程

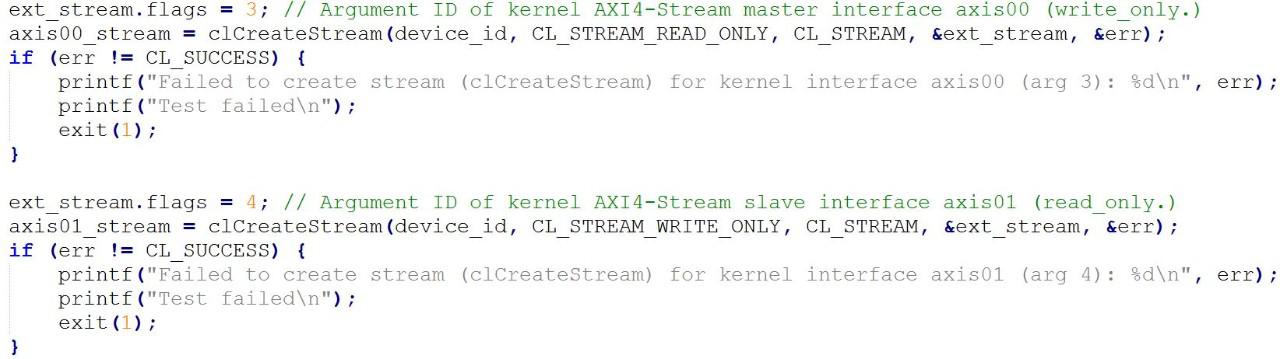

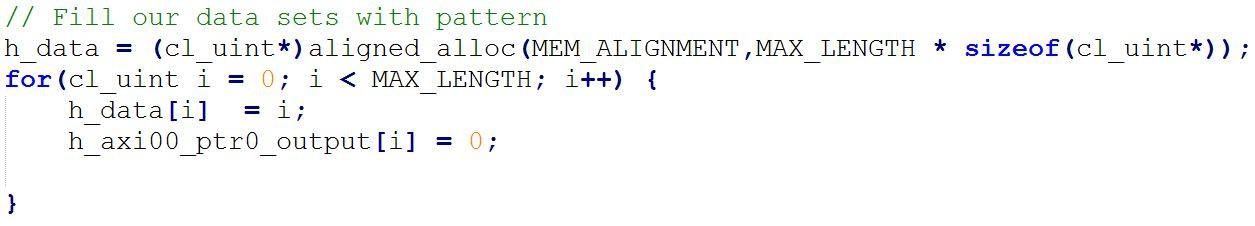

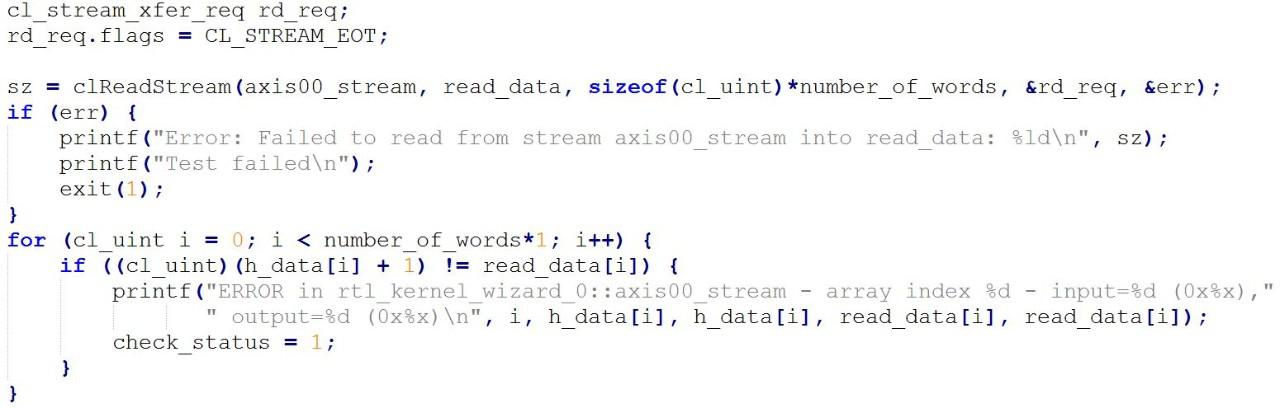

主机示例代码创建内核,为主机中的标量和 AXI Stream 分配存储器,分配发送到 GT 内核的出口数据,从 GT 内核读取入口数据,并将读取的数据与初始数据进行比较。下面的代码示例取自示例应用,用户可以修改出口数据分配。

- 将参数设置为内核函数调用

- 分配 AXI4 Stream:axis00(主、入口)和 axis01(从、出口)

- 将用户数据模式分配给 h_data(出口数据)

- 内核函数调用,并将入口数据与用户数据模式 (h_data) 进行比较

在服务器上的 Alveo U200 卡(目标平台)上运行应用

结论

Vitis 软件平台提供了一个向基于处理器的系统添加用户内核的易于理解的设计流程 GUI。由于 FPGA 配备了硬处理器,因此这种设计方法使得用户能够定制基于收发器的设计。

有了 Vitis 环境中的预定义 shell 和内核,用户可以通过 C 代码创建定制逻辑和数据模式来进行设计验证。此外,该流程还为 FPGA 逻辑设计师提供了参考平台,他们可以通过 RTL 内核向导创建不同的内核。

资源

Alveo U200 数据中心加速器卡:

https://www.xilinx.com/products/boards-and-kits/alveo/u200.html

赛灵思运行 时和部署 Shell 下载:

https://www.xilinx.com/products/boards-and-kits/alveo/u200.html

UG1301 (Alveo 入门指南):

赛灵思 UltraScale 和 UltraScale+ 收发器用户指南:

https://www.xilinx.com/support/documentation/user_guides/ug578-ultrascale-gty-transceivers.pdf

https://www.xilinx.com/support/documentation/user_guides/ug576-ultrascale-gth-transceivers.pdf