使用 ChipScope 在 Alveo 数据中心加速器卡上调试应用

介绍

赛灵思 Vitis™ 统一软件平台在仿真和硬件执行流程方面提供了应用级调试功能和技术。本文重点介绍在 Alveo™ 数据中心加速器卡上调试设计。有时,设计可以通过硬件仿真,但在实际硬件平台上运行时仍存在一些问题。在这种情况下,我们可以采用赛灵思 ChipScope 工具进行板载调试。

如果您有FPGA硬件开发经验,您可能会很了解ChipScope,因为它是在 FPGA 上执行调试的一种非常常见的方法。您可以将它与 Vitis 流程结合使用,但您必须对ChipScope工具有所了解。您可以在《Vivado设计套件用户指南:编程和调试》 (UG908) 中了解有关它的更多信息。

在 Vitis 流程中,有两种方法可以插入 ChipScope 核来调试您的内核:

- 在内核接口上使用自动插入的系统 ILA 核调试应用

- 使用手动添加的 Chipscope ILA 核调试应用(仅适用于 RTL 内核)

这两种情况将在以下部分中演示。

注意:以下部分提供了关于如何在 Alveo 卡上调试加速项目的说明,但它们并没有涵盖 Vitis 或 Vivado 工具基本操作的每个细节。如需了解有关在 Vitis 或 Vivado 中执行操作的更多信息,请参阅赛灵思网站上的其他文档。

在内核接口上使用自动插入的系统 ILA 核调试应用

设置您的环境

为了设置您的环境,请执行以下操作:

- 打开 Vitis IDE,从您拥有的平台中选择一个您想用来测试应用的平台。

- 创建一个新的应用项目,并从 Vitis 加速示例中选择“loop reorder”模板。在此案例中,以该模板为例;您可以选择任何其他适用的应用

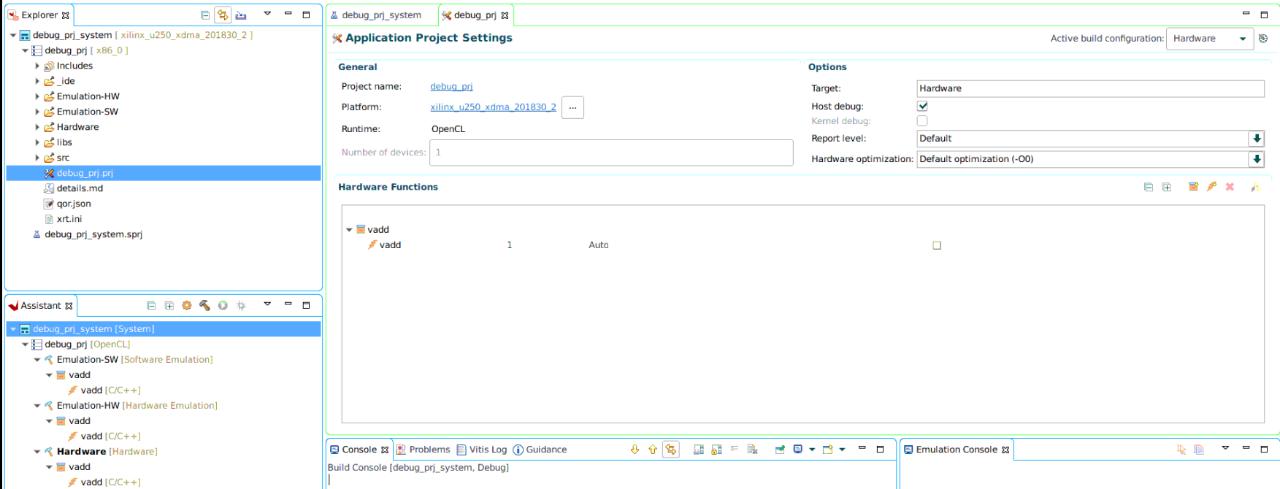

- 选择 hw 作为活动构建并启用主机调试。在本案例中,需要启用主机调试选项,以便在连接到硬件服务器时执行 GDB 调试操作。

该项目应类似于以下内容。

构建目标

要构建目标:

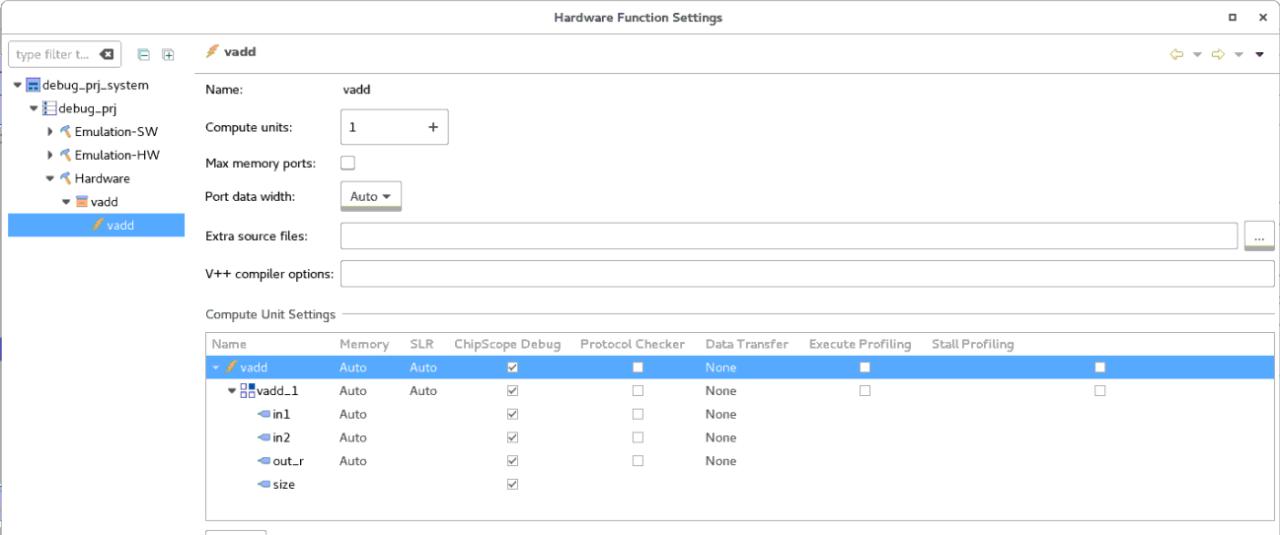

- 设置内核以启用 ChipScope 核插入。

2. 构建 hw 目标,这需要一些时间才能完成。

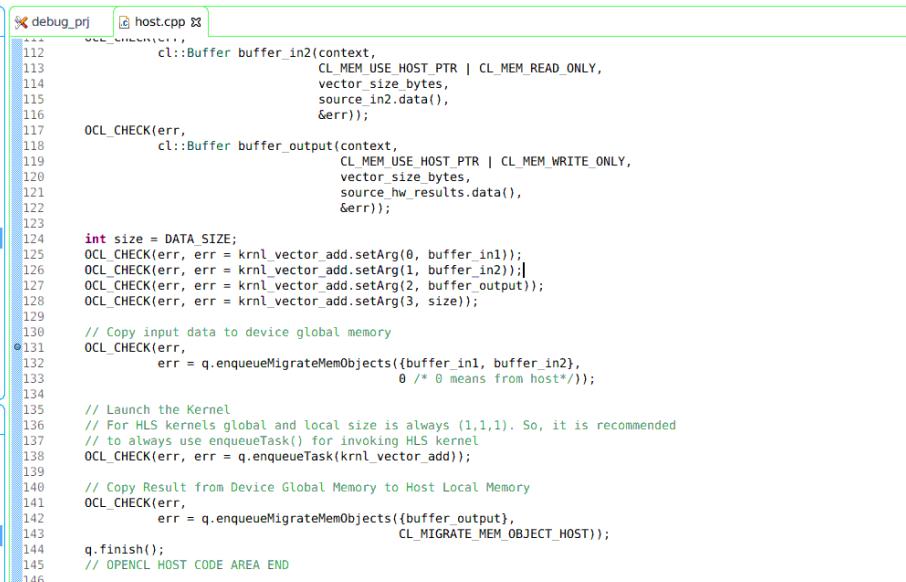

3. 打开主机代码并设置断点。

在本案例中,断点是在启动内核之前(第 131 行)设置的,但是您可以选择任何其他位置。

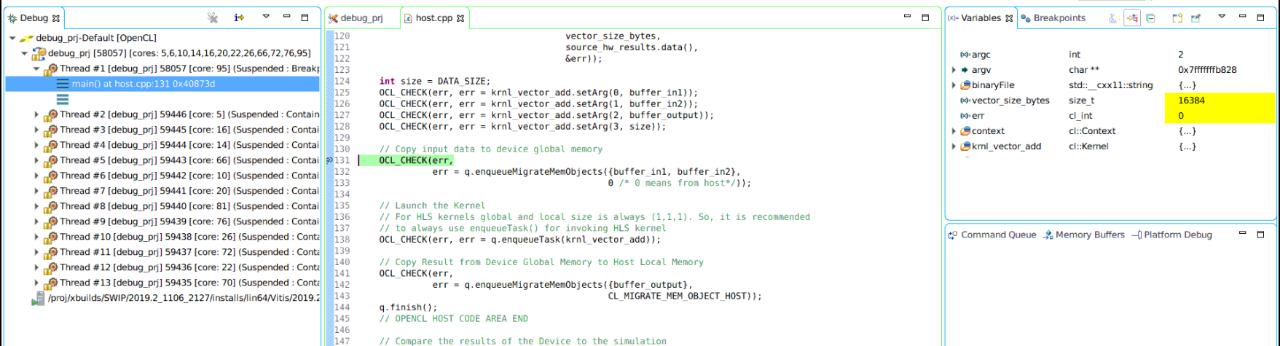

4. 单击“调试”工具栏按钮,在“调试”透视图中启动您的应用。

应用在主函数项处暂停。

5. 单击“恢复”按钮以恢复应用。

它在上一步中您添加的断点处暂停。

此时,您可以执行标准的 GDB 调试操作来调试您的主机应用。对于本案例,我们将重点介绍如何使用 ChipScope 在板上调试内核,因此我们只需使用此断点在内核执行之前将主机应用暂停在某个位置,以便设置 ChipScope 环境。

您还可以使用其他方法暂停主机应用,例如添加一段代码段。如需查看示例,请参阅 Vitis 文档中的在启动内核之前添加 ILA 触发器。

连接到硬件服务器

Alveo 卡设置的常见情况是安装在主机的 PCIe 插槽中,所有用户通过以太网连接到主机。在这种情况下,可采用赛灵思虚拟线缆 (XVC) 技术对 Alveo 卡进行编程和调试。XVC 允许 Vivado 通过以太网传输 JTAG 命令来编程和调试 FPGA。XVC 服务器必须设置在连接到 FPGA 卡的本地主机上。Vivado 硬件管理器会话可以在其他机器上启动并远程连接到该服务器。

- 输入以下命令,打开一个新的终端来设置 XVC 服务器:

debug_hw --xvc_pcie /dev/xvc_pub.

如果此命令成功执行,您将看到终端窗口中显示与下图类似的消息。

- 在第三个终端中打开 Vivado 并使用以下命令连接到 XVC 服务器:

debug_hw --vivado --host

注意: 如果 Vivado 硬件管理器与 XVC 服务器在同一台机器上启动,请使用 localhost 作为主机名。filename.ltx 是调试探测信息的文件,通常与 xclbin 文件位于同一文件夹中。

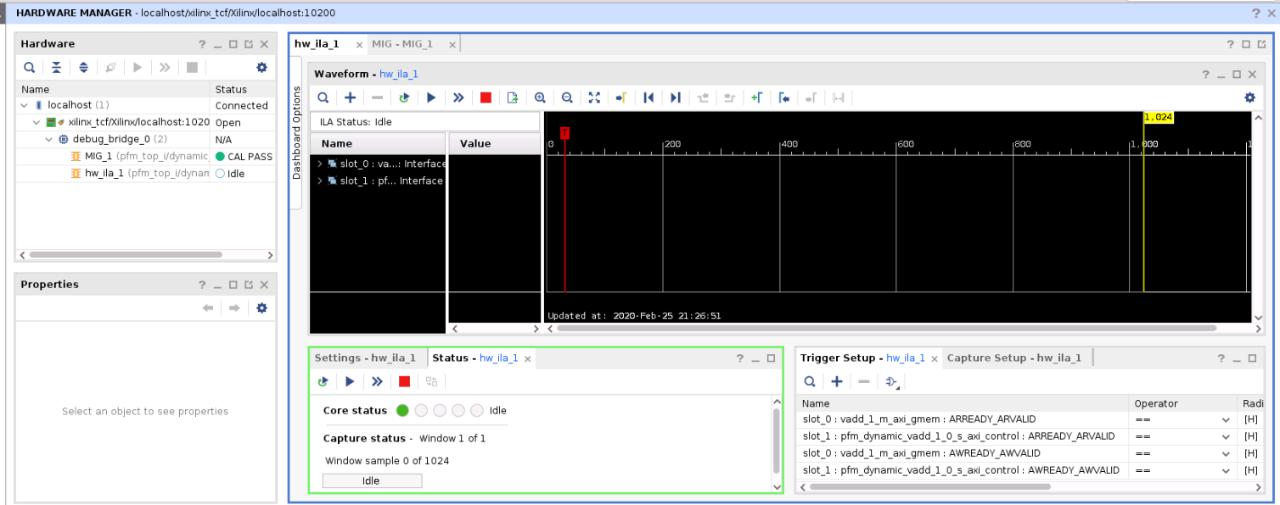

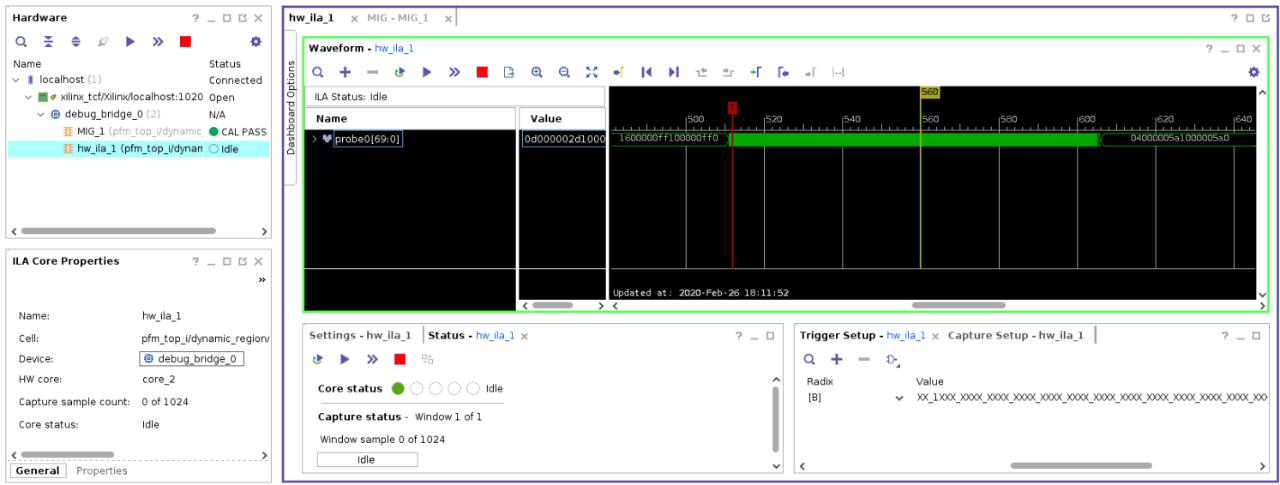

如果一切都设置正确,您应该可以在 Vivado GUI 中看到两个 ILA。一个是预构建的 MIG_1 核,另一个名为 hw_ila_1 的核是由 Vitis 工具插入的系统 ILA 核。

调试您的应用

现在,您必须设置 ILA 触发条件。

- 对于本案例,使用 AXI 主接口的 ARVALID 信号作为触发信号,并在 ARVALID 为 1 时捕获数据。您可以根据需要捕获的数据场景定义其他适当的触发条件。

- 当您完成触发条件的设置后,单击“运行”。ILA 变为“等待触发”状态。

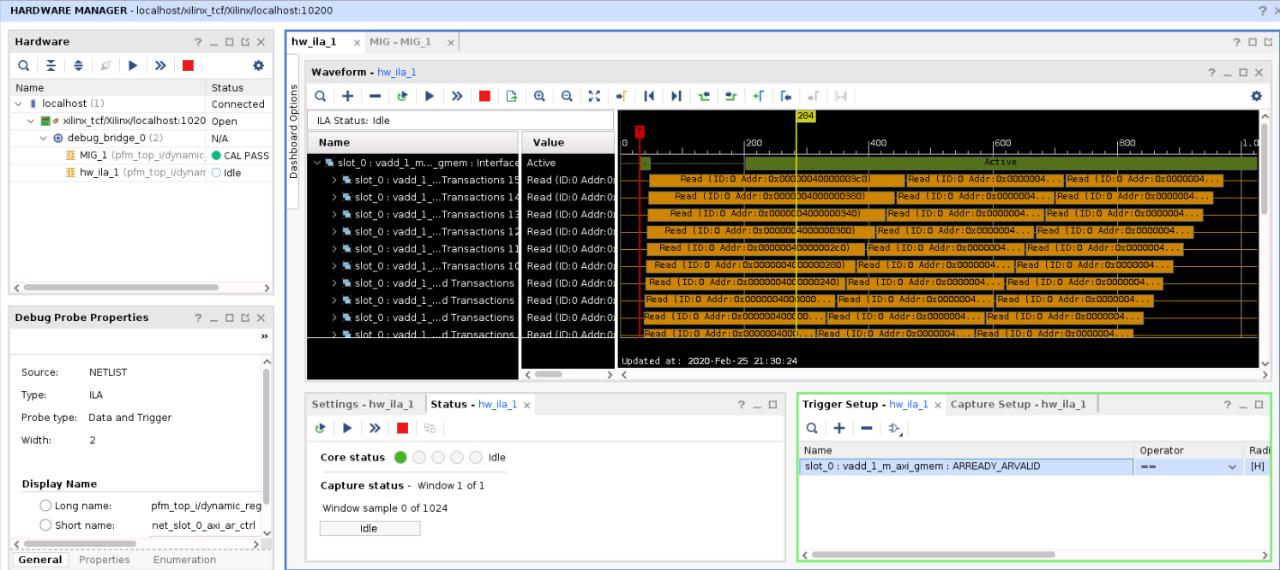

- 返回到您的 Vitis 项目并单击“恢复”以继续运行主机应用。如果没有设置其他断点,主机应用应一直运行到最后并打印“测试通过”信息。

- 切换回 Vivado 硬件管理器对话框。ILA 应处于触发状态,如果一切正常,则转储并显示信号波形。

使用手动添加的 ChipScope ILA 核调试应用(仅适用于 RTL 内核)

对于 RTL 内核设计,诸如 ILA 和 VIO 这样的 ChipScope 核可以像传统 FPGA 设计一样在 RTL 代码中实例化。通过这种方式可以探测内部信号,在内核内部提供更多可见性。需要具备硬件设计知识才能完成这项技能。此外,选择合适的探测信号对提高探测效率也非常重要;但是,这不在本教程的范围内。

设置您的环境

为了设置您的环境,请执行以下操作:

- 创建一个新的 Vitis 应用项目并选择“空”模板。

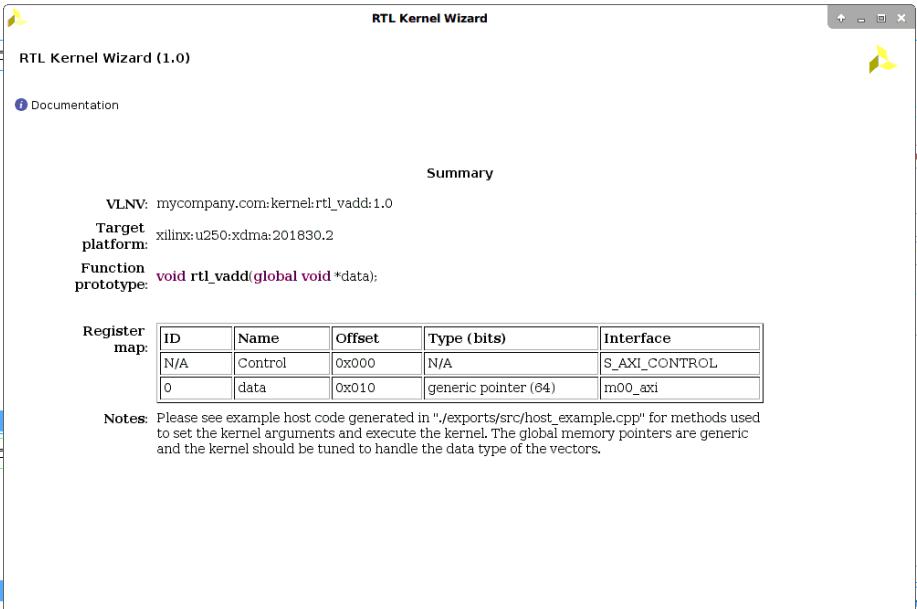

我们将使用 RTL 内核向导创建一个简单的 RTL 内核。为简单起见,此演示仅选择一个 AXI 主存储器端口。摘要页面应类似于下图:

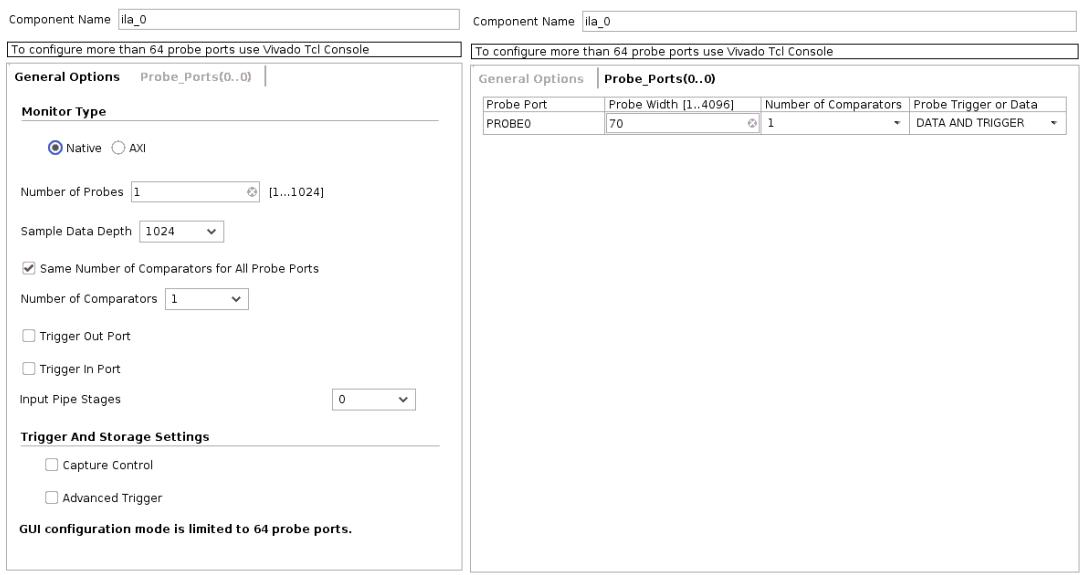

2. 使用 ILA 配置在 IP 目录中创建一个 ILA 核,如下图所示:

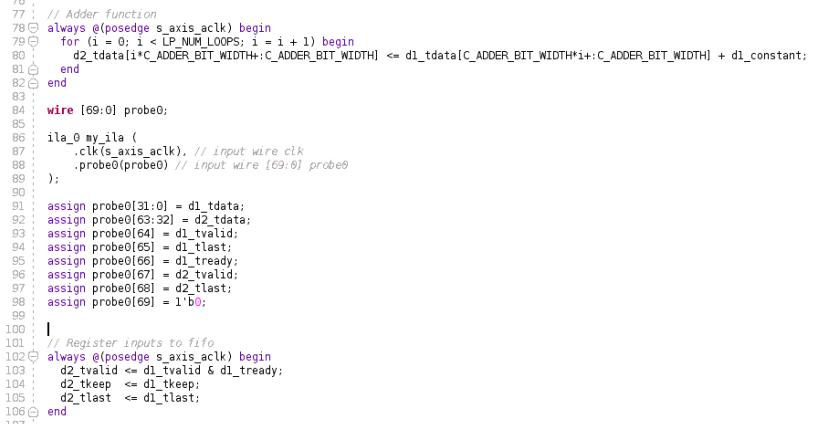

3. 在创建的 RTL 内核示例项目中,修改 rtl_vadd_example_adder.v 文件以插入您刚才创建的 ILA 核。

4. 在设计中实例化 ILA 核并与探测信号建立连接。

修改后的代码如下:

5. 单击左侧面板中的“生成 RTL 内核”按钮并关闭 Vivado 项目。

构建目标

- 在 Vitis 应用项目中构建 hw 目标。

注意: 这可能需要一些时间来完成。

RTL 内核向导在 src 文件夹中提供了一个示例主机代码。

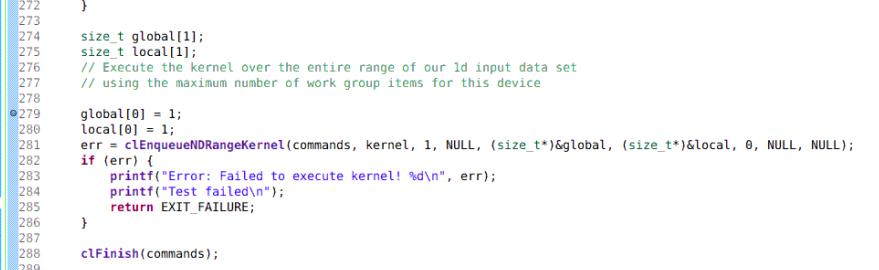

2. 打开主机代码并添加断点。

例如,我们可以在启动内核之前在第 279 行添加一个断点。

连接到硬件服务器并设置触发器

- 设置 XVC 服务器并打开 Vivado 硬件管理器。

- 将 probe0[67] 设置为触发条件,并用它来捕获 d1_tdata 和 d2_tdata 信号,如调试您的应用中所述。

ILA 应处于触发状态,并转储和显示信号波形。

提示

- 在主机代码中设置断点时,最好在 xclbin 加载命令之后设置。当 xclbin 加载到 FPGA 后,启动 Vivado 硬件管理器,以获取更新的调试核信息。

- 如果您修改了 ChipScope ILA 信息,并且更改没有反映在 Vivado 中,请尝试关闭 Vivado 硬件管理并重新启动以再次连接到目标。同时,.ltx 文件需要与设计中的 ILA 探测相匹配;否则,调试信息可能不正确。

总结

尽管您可以依靠硬件仿真来解决大多数功能性问题,但对于 Vitis 设计,板载调试是一项必不可少的强大功能。Vitis 利用 ChipScope 工具提供了一种探测内核的方法。

可以使用 Vitis 命令中的 dk 选项插入系统 ILA 来探测内核接口。这是一种简单且自动执行的方法,不需要任何硬件知识。它支持所有类型的内核。

对于 RTL 内核,您还可以按照传统的 RTL 设计调试方法在内核中插入 ChipScope 核。这需要一点 RTL 知识和硬件设计经验。