Analogic与Orthogone合作开发的高性能医学数字成像检测器技术

概述

了解 Orthogone Technologies 如何使用赛灵思 Zynq UltraScale+ MPSoC 和 Artix-7 FPGA 为提出了大量多学科技术挑战的医学成像应用开发最先进的数字平台。

简介

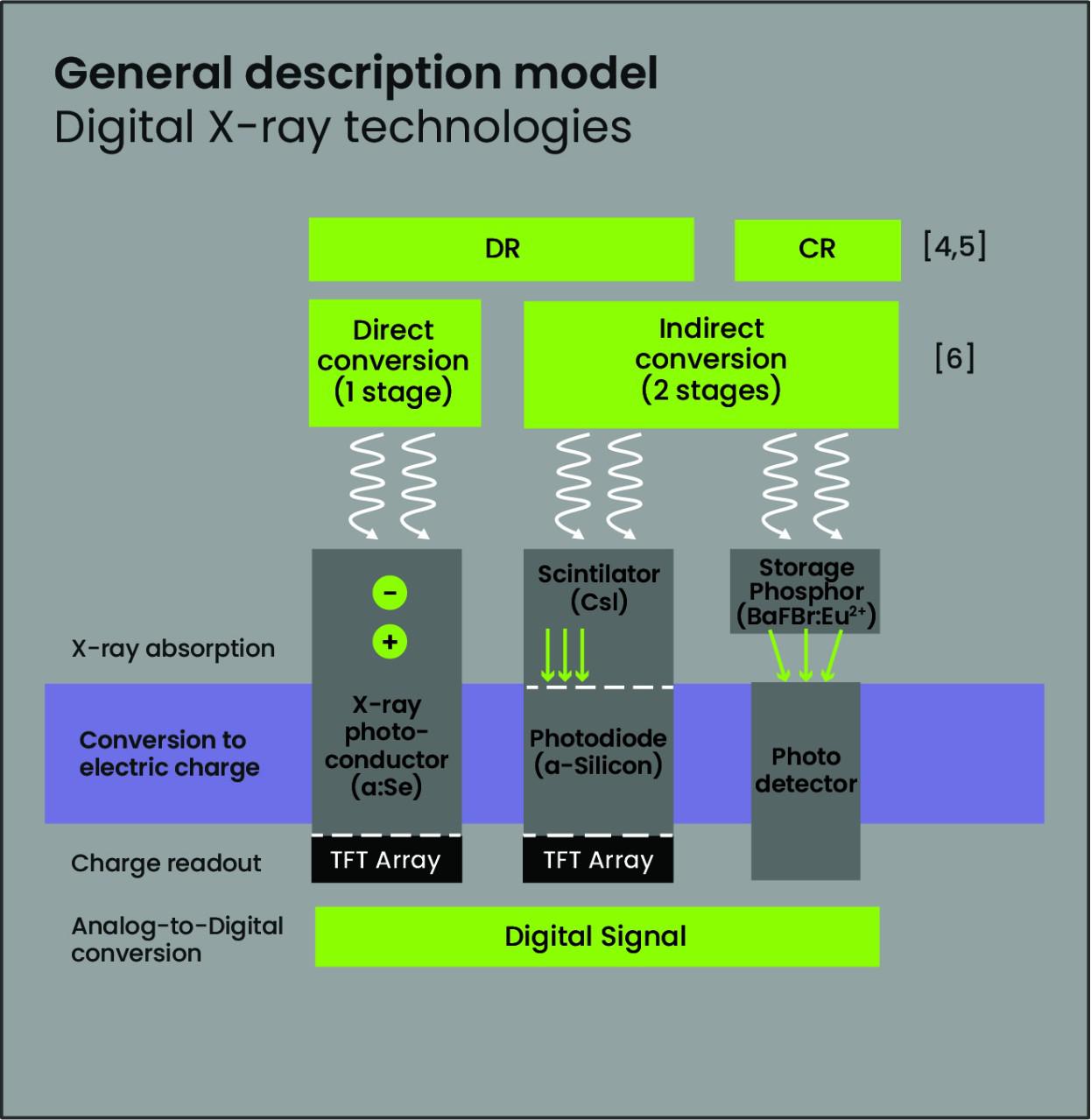

作为直接转换数字检测器技术的全球领先者,Analogic 开发和制造了平板直接转换数字检测器,主要由医疗原始设备制造商应用于乳房 X 线照相术系统。Analogic 开发的平板将图像数据直接捕捉到由薄膜晶体管阵列上沉积的非晶硒层制成的专利检测器上。与传统的 2D 胶片乳房 X 线照相术相比,Analogic 的检测器技术实现了提供 3D 图像的数字化断层融合,这提高了读取精度,减少了假阳性。

Analogic 需要特定的专业知识才能使其专利检测技术利用高性能图像处理算法。由于会有不同的制造商在一系列设备上使用 Analogic 检测器,因此系统架构的设计需要具有通用性且易于集成,这是首要要求。因此引入了 Orthogone 产品开发团队作为合作伙伴,以提供所需的专业技术并加快开发周期。Orthogone 经验丰富的 FPGA 设计师、嵌入式软件设计师和硬件设计师与 Analogic 团队合作开发出了新的检测器解决方案。

使用赛灵思组件克服技术挑战

为乳房 X 线照片、3D 乳房 X 线照相术和其他医学成像应用开发最先进的数字 X 射线平台带来了各种多学科技术挑战,包括设计一个可以支持多种传感器配置的灵活且可扩展的图像重建处理引擎。

团队决定使用赛灵思 Zynq UltraScale+ MPSoC 来提高性能,并使用其他赛灵思 FPGA 来提供灵活性并加快开发时间。软件和 FPGA 能够轻松集成到直观的具有多个 AXI4 接口的整体设计环境中,这是选择赛灵思而不是其他竞争技术的关键原因。此外,赛灵思评估板和参考设计还帮助团队快速启动设计并在收到 PCB 之前消除大部分设计的风险。

本文介绍了各种挑战以及在项目多个部分的技术解决方案中使用的赛灵思组件:

- 系统设计与架构

- 图像处理

- 硬件设计

- 软件设计

系统设计与架构

为了使平板检测器对患者更安全、读数更准确,系统设计师和设计架构师必须将具有高速数字处理功能的超灵敏传感器集成到高度集成的薄型外壳上。

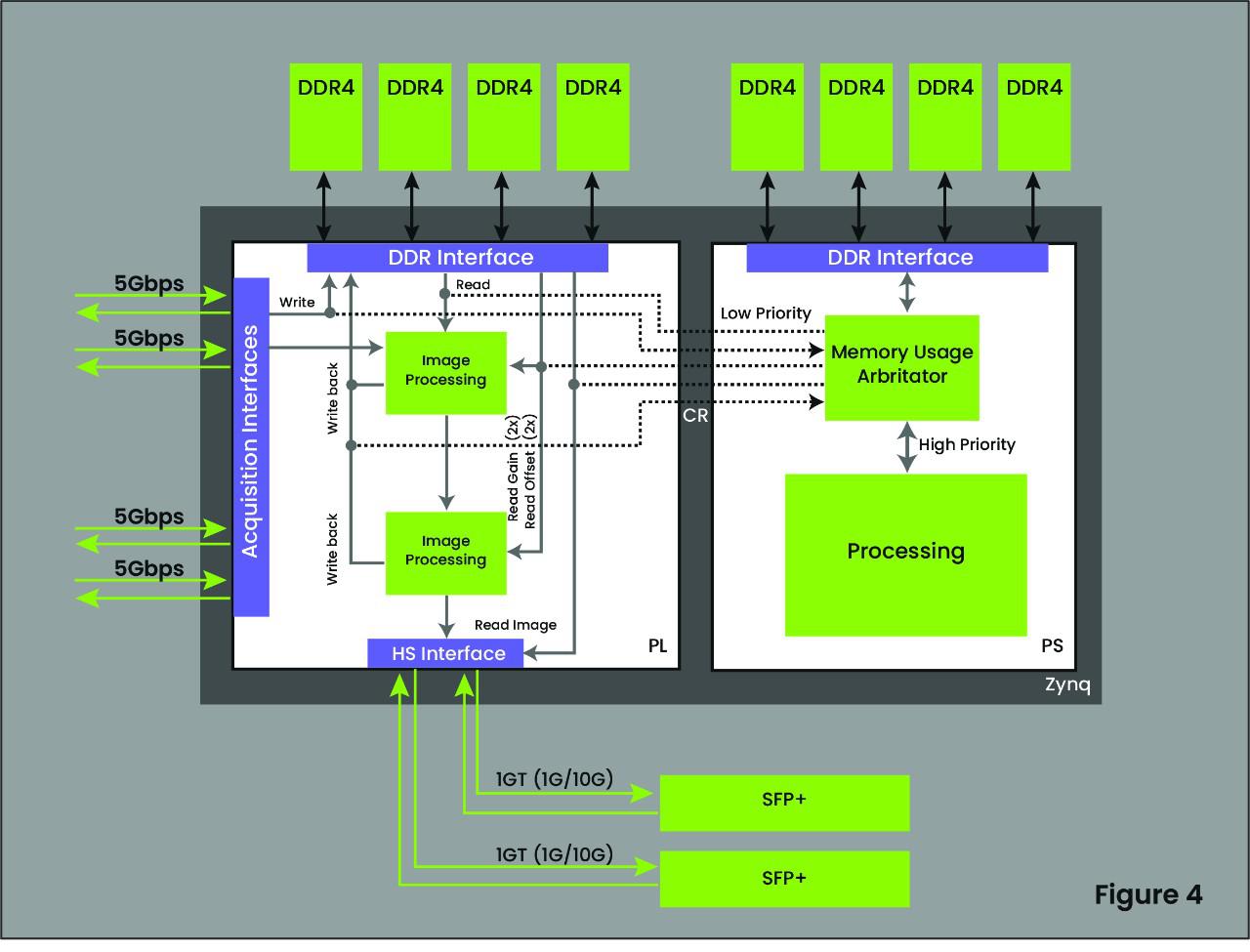

图像采集过程的第一步是从传感器获取高速原始数据。根据传感器的分辨率和所需的帧率,可能需要支持超过 10Gbps 的读出速率。大面积平板通常由多个传感器组成,这些传感器组合在一起形成更大的高分辨率图像。原始图像数据通常通过多个高速链路从传感器传输。

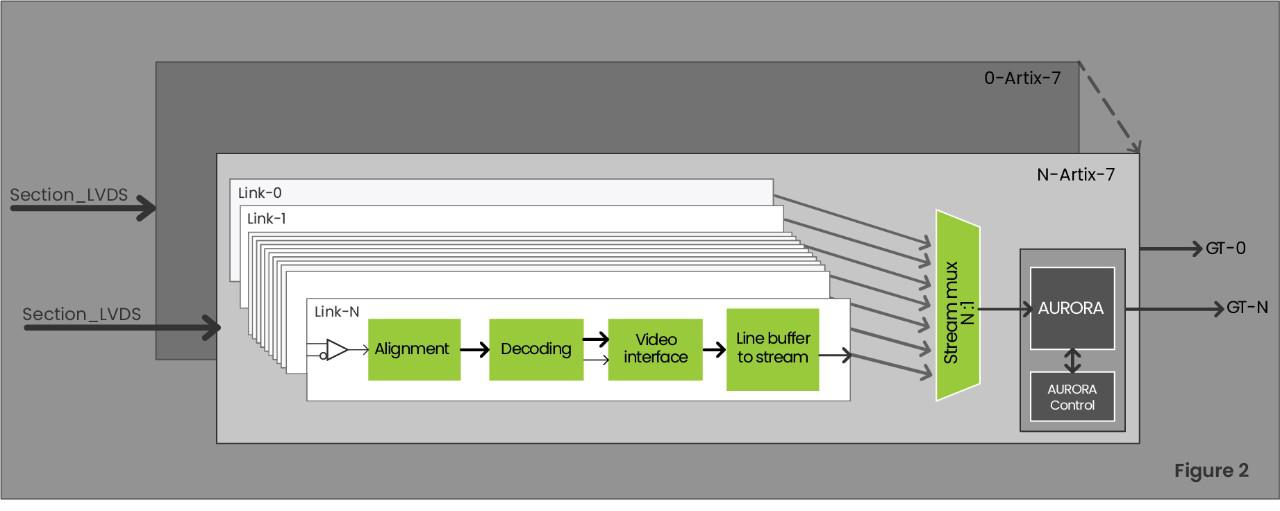

对于这种应用,乳房 X 线照相术传感器被分成多个独立的部分,每个部分都使用多个高速 LVDS 差分对来传输它们的原始采集数据。为了避免运行多个可能导致过多串扰和噪声的长 LVDS 链路,我们选择将原始数据传输到独立的低功耗赛灵思 Artix-7。我们使用此方案将每个 FPGA 放置在靠近其各自部分的位置,从而缩短了 LVDS 链路并显著减少了 PCB布线拥塞。

Artix-7 安装在位于 PCBA 中心的 MPSoC 周围,并使用薄型连接器和柔性电缆/PCB 与每个部分接口连接。各 Artix-7 接受原始数据,解码传入的流,将它们进行汇集并使用路由到 MPSoC 的千兆位收发器 (GT)执行数据序列化。

赛灵思 Zync UltraScale+ MPSoC 将 Kintex UltraScale+ FPGA 可编程架构与包含 64 位双核 Arm® Cortex®-A53 和双核 Arm Cortex-R5的处理系统 (PS) 集成到单个器件上。使用赛灵思 MPSoC 有几个优势,包括集成了与 FPGA 架构紧密耦合的多核 ARM 处理器。我们选择这种架构是为了从 FPGA 架构性能和使用多个 ARM 核的灵活性中获益,其中一些 ARM 核可以与医疗行业所需的关键性应用的操作系统(需要进行认证)配合使用。此外,多个高速外设控制器(如 SATA 和 USB 3.0)可直接集成到 Zynq MPSoC中。

“由于产品的使用寿命相对较长,因此选择具有长期可用性的关键组件非常重要。赛灵思设计产品并创建支持性供应链,其明确目标是保证从第一个产品版本开始,在至少 15 年以上的生命周期内提供支持。” – Alexandre Raymond,Orthogone Technologies首席技术官

图像处理

如前所述,每个 Artix-7 FPGA 都与各自的部分接口连接。在主机软件发出全局触发信号后,所有部分将其原始数据发送至各自的 Artix-7 FPGA。

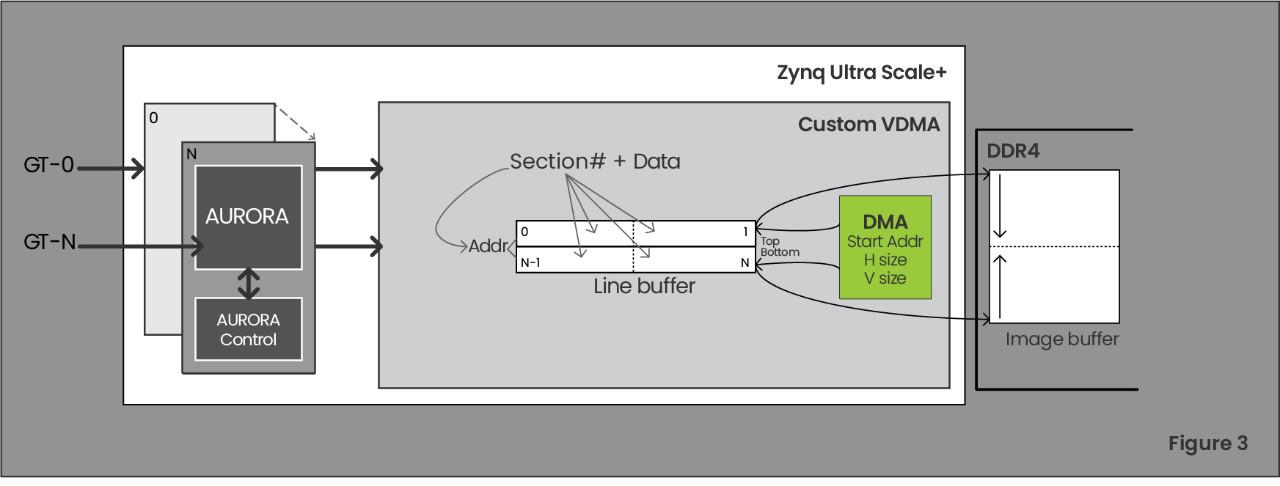

每个 Artix-7FPGA 同时对齐和解码传入的数据,并将其写入一系列使用模块 RAM (BRAM)) 存储器实现的行缓存。缓存的数据接下来被多路复用并打包到单通道 5Gbps Aurora 链路。赛灵思的 Aurora IP 在CRC 支持下生成,以保证数据的完整性。在串行链路的另一端,接收器以 CRC 错误标记任何传输,并请求重新尝试连接至 Artix-7 FPGA Aurora 接口。

Orthogone 设计了一种可轻松适应不同传感器尺寸的可扩展架构。

该架构可容纳多个部分配置,这使得它具有很强大的可扩展能力;而定制 VDMA 在外部存储器中重新组织完整的图像。当图像的所有像素均正确地完成重新排序后,FPGA 就可以执行额外的图像处理操作来增强图像的质量。使用平场校正型处理可以轻松去除固定模式噪声。

赛灵思 Zynq UltraScale+ MPSoC 提供了大量可用于对已捕获数据执行图像处理的 DSP 模块资源。该平台使用的是包含 1728 个 DSP Slice 的 ZU7CG MPSoC 器件。每个 DSP Slice 基本上由一个专用于 27×18 位二进制补码乘法器和一个 48 位累加器组成。为逐帧执行乘法、加法/减法,可以轻松实现平场校正和其他图像处理算法。处理模块可以将图像数据路由到 DDR,或直接路由到后端接口,后者将通过 UDP 会话在 10G 以太网端口上传输图像/视频内容。

硬件设计

在为最苛刻的医疗应用设计超高性能数字 X 射线产品时,硬件设计师面临着一些挑战,包括最大限度减少噪声、将高速数字电路与超低噪声电路集成、实际尺寸限制、安全考虑等。

结合使用低噪声降压变换器和稳压器来降低 EMI 并提供低噪声稳定 DC 轨。赛灵思 Zynq 能够监测和控制所有板载电源,并在需要时禁用不必要的电源轨,以降低功耗。

赛灵思 Zynq UltraScale+ MPSoC 是系统的核心,负责检索来自 Artix-7 FPGA 的图像传感数据,并创建将发送到通过高速光收发器接口连接的外部计算机的最终图像。本地帧缓存存储在 DDR4 存储器中,可用于重建和帧缓存。

选择 DDR4 的原因是出于对速度和功耗的考虑,所有需要的校准都由赛灵思 MIG 自动完成。DDR4 存储器的架构设计支持以非常快的帧率采集多帧(图像/系数)运动。

赛灵思 Zynq UltraScale+ FPGA 有几种启动模式,该电路板针对 QSPI32 和 JTAG(出于开发和调试目的)进行配置。QSPI Flash 连接到 Zynq 的 PS 侧,将从此处启动并对 FPGA 进行编程。QSPI Flash 包含 FPGA 位文件和软件启动代码。第二个 QSPI Flash 用于记录错误和其他信息。

此外,PS 的 SATA 接口上也有一个 SSD 驱动器。此驱动器包含在每个处理器(Linux、MEL、实时)上运行的不同应用、备份 FPGA 位文件和检测器配置。

软件设计

在 Zynq UltraScale+ 硬件平台上运行的 Analogic 检测器软件被分为不同的应用。这些应用在 FPGA 侧管理图像数据路径的实时控制并使用 Linux 执行非关键后台任务。

Zynq MPSoC 硬件平台使用多个可访问私有和共享存储器区域和外设的处理器。以 Mentor® 嵌入式多核框架 (MEMF) 库为基础,大多数处理器间消息传递都通过系统共享存储器进行。它使用一种为多处理器系统开发的称为“rpmsg”的机制。这种机制使用中断和共享存储器在多个处理器之间接收和发送消息。

在 Zynq UltraScale+ 硬件平台上运行的 Analogic 检测器软件被分为不同的应用。这些应用在 FPGA 侧管理图像数据路径的实时控制并使用 Linux 执行非关键后台任务。

Zynq MPSoC 硬件平台使用多个可访问私有和共享存储器区域和外设的处理器。以 Mentor® 嵌入式多核框架 (MEMF) 库为基础,大多数处理器间消息传递都通过系统共享存储器进行。它使用一种为多处理器系统开发的称为“rpmsg”的机制。这种机制使用中断和共享存储器在多个处理器之间接收和发送消息。

结果

通过创新设计和技术使用,Orthogone 与 Analogic 合作开发出了一种解决方案,它提供的通用性和易用性有助于产品在其延长的产品生命周期内保持其竞争优势。如需了解有关与 Orthogone 合作的更多信息,请参见外包工程服务。

Arm 和 Cortex 是 Arm Limited(或其子公司)在美国和/或其他地方的注册商标。

Mentor 是 Mentor Graphics Corporation 的注册商标。