Vitis AI 加速 GMSL摄像头人脸检测 - 第二部分

原型系统

赛灵思 ZCU102平台与Avnet FMC- multi - cam4 FMC 结合部署。默认系统只使用四个摄像头中的一个进行处理。利用OpenCV下的V4L2从摄像头信号捕获画面帧,然后将画面帧通过Densebox神经网络传递给DPU进行人脸检测,并使用OpenCV绘制边界框。最后将输出帧传递给Gstreamer流水线,该流水线将通过 PS 显示端口输出。

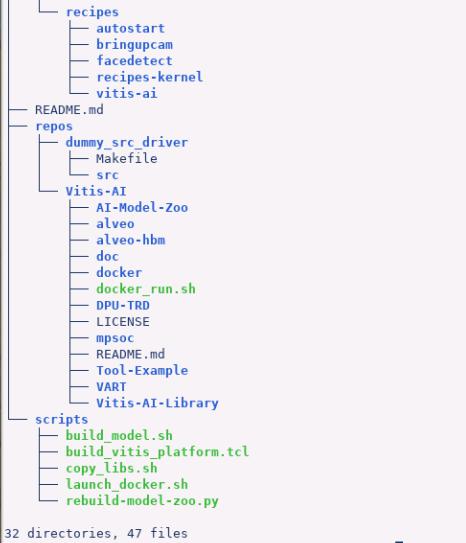

项目组织

此设计流程涉及诸多工具和存储库,它们通过传递特定设计文件进行交互。因此,整理好设计文件对于避免混淆至关重要。本教程对源文件、配置文件和构建脚本使用以下组织方法

通常,设计源文件分为 hardware 目录和 petalinux 目录,每个目录都包含与其构建部分相关的源代码、脚本和配置文件。此外,boot 目录包含用于创建 BOOT.BIN 的 .bif 文件。doc 目录包含此文档。

dpu 目录包含与 DPU 配置相关的文件,这些文件会在构建和执行期间的不同时间受到抓取。repos 目录包含构建期间使用的依赖存储库的本地副本。最后,scripts则 包含其他杂项脚本。

在构建过程中,还将创建以下目录

- vitis_platform_workspace—创建平台的Vitis工作区

- sd_card -放置所有二进制文件的最终输出目录

FPGA 设计

FPGA 设计实现了两个主要功能:一是具备预处理的图像采集流水线;二是 DPU 加速。

要构建 FPGA 设计,请遵循以下步骤:

1. 设置环境

source

2. 运行创建 Vivado 项目、导入源代码、构建 IP 集成器设计并生成比特流的脚本

make hardware

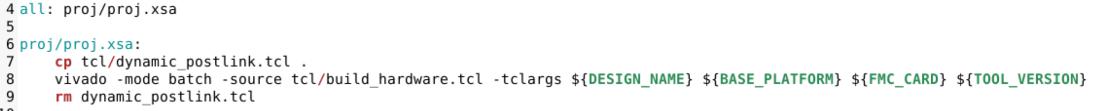

主生成文件调用硬件目录中的子生成文件。后一个目标如下所示

主要任务是使用 hardware /tcl/build_hw.tcl 调用 Vivado,它执行以下操作:

1. 设置正确的电路板或部件号

2. 在 hardware 目录中创建一个项目

3. 导入 HDL 源

4. 导入 XDC 约束

5. 使用源 hardware /tcl/bd/bd_zcu102_avnet_gmsl_2019.2.tcl 构建块设计

6. 为块设计生成包装和输出产品

7. 运行综合

8. 使用附加的 Vitis 元数据属性标记设计

9. 附加 dynamic_postlink.tcl

Due to Vitis expectation of relative file, 由于 Vitis 对相关文件位置的预期,hardware /tcl/dynamic_postlink.tcl 会暂时复制到 hardware 根目录。稍后将描述 hardware /tcl/dynamic_postlink.tcl 的用途和功能。

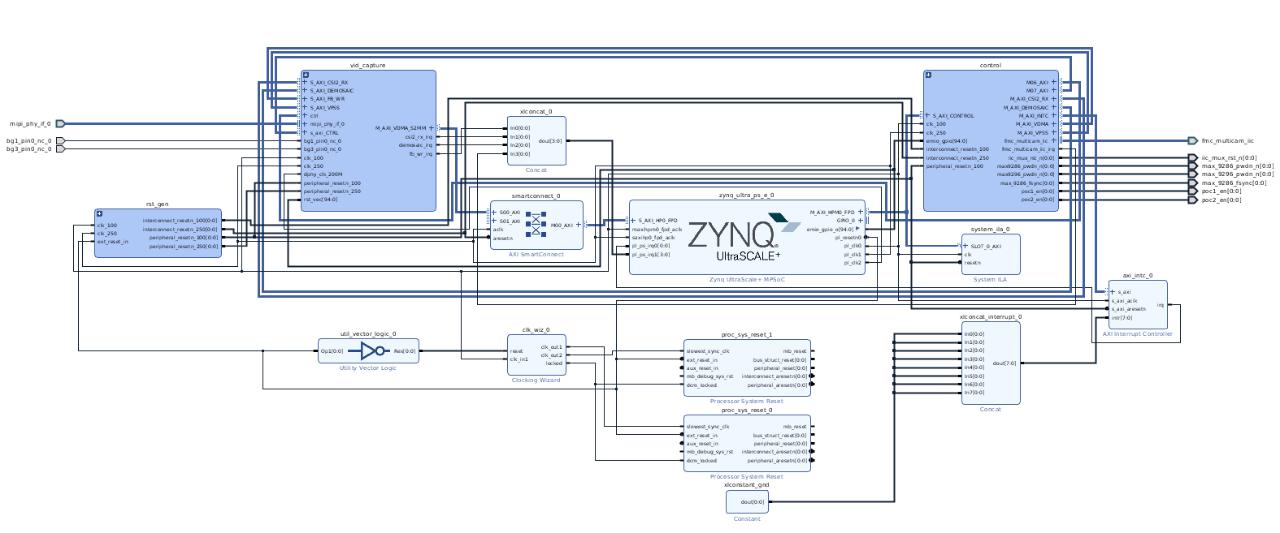

Vivado 项目概述

Vivado 项目已存在于 hardware/pro j中,可以用 Vivado project .xpr打开

vivado proj.xpr

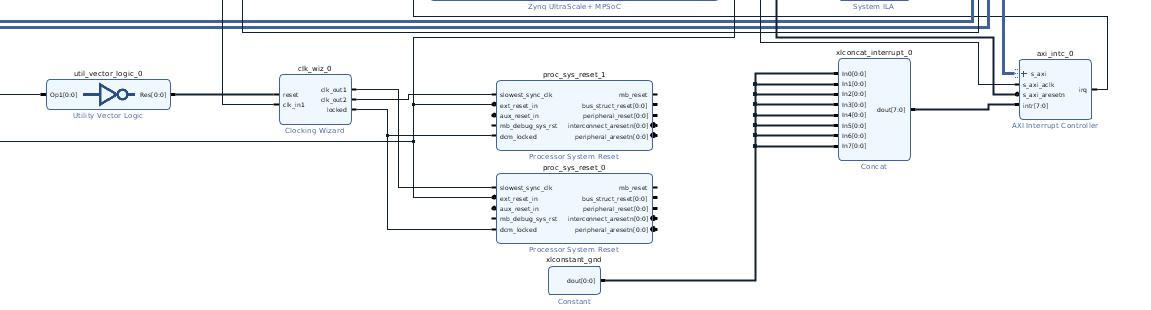

Vivado 的顶层块设计如下所示

有用于图像捕获流水线 (vid_capture)、控制逻辑 (control) 和复位生成 (rst_gen) 的分层块。 Zynq Ultrascale+ MPSoC 模块具有以下关键配置

- M_AXI_HMP_FPD 已启用并连接到包含 AXI 互连的控制块,用于访问设计中使用的所有控制接口

- pl_clk0 是一个 100MHz 的通用时钟,驱动控制逻辑

- pl_clk1 是一个 250MHz 时钟,驱动 AXI 流视频逻辑

- pl_clk2 是一个用于 MIPI DPHY 的 200MHz 时钟

- S_AXI_HP0_FPD 已启用并连接到视频捕获流水线的 DMA(帧缓冲区写入)

- pl_ps_irq0 为 DPU 中断逻辑启用

- pl_ps_irq1 由系统中的其他中断使用

下面再次展示的逻辑子集将添加到平台设计中使用。

它由时钟、复位和中断设置组成,这些设置由 Vitis 识别并在流程后期自动连接到硬件加速器(即 DPU)。在这一阶段,我们只需要确保它们已包含在设计中,并使用适当的元数据进行标记,以便 Vitis 能够发现它们及其属性。后续我们会对其进行深层次的讨论。

使用预处理的图像捕获流水线

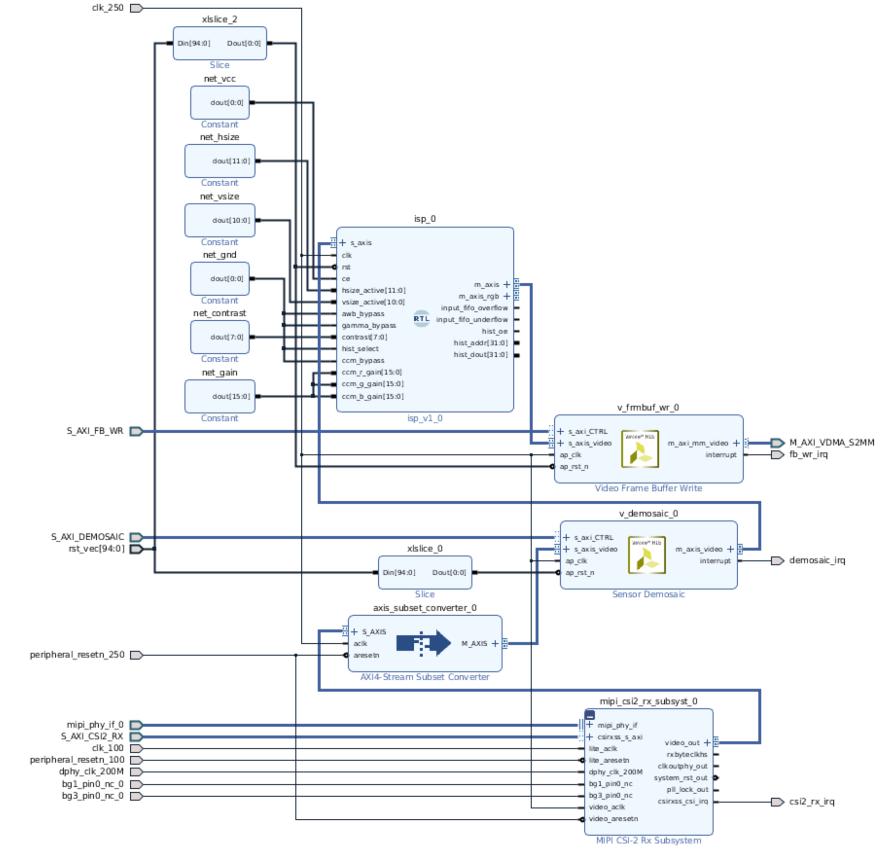

vid_capture 块包含图像捕获流水线和相关的预处理,将在图像上完成此类预处理以供 DPU 使用。

MIPI CSI2 RX 子系统连接 FPGA 引脚并实现 MIPI CSI2 接收器控制器。它将视频数据转换为 AXI 流输出。由于图像传感器输出 12 位数据,因此首先使用 AXIS 子集转换器来选择所需的 8 个 MSB。 传感器发送需要转换为 RGB 的 RAW Bayer 数据,这一转换在 v_demosaic_0 块中进行。接下来,插入一些小型 ISP 功能以提高图像质量。最后,使用 Framebuffer Write IP 将数据直接存储到内存中。

DPU 加速

设计的这一阶段尚且不包括 DPU IP,而是在设计流程的后期由 Vitis 自动插入。虽然看起来或许很奇怪,但这样做的原因在于 DPU 配置可以在Vitis环境中反复更改,无需接触 Vivado 设计。因此设计环境更为灵活,对缺乏传统 FPGA 设计经验的用户较为友好。

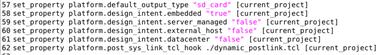

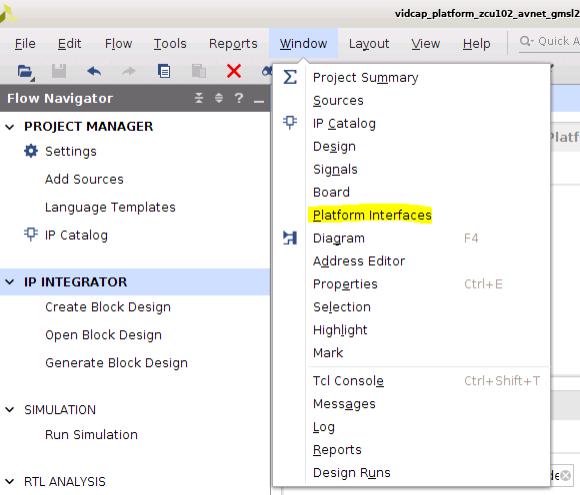

为便于该流程操作,设计的各部分都使用某些属性进行标记,这些属性在.xsa文件中以元数据的形式呈现。此类元数据将由 Vitis 解析,以便部署加速器。其中包括可用于加速器使用的接口、时钟、重置和中断。要查看 Vivado 中的这些元数据“标签”,请选择Window -> Platform Interfaces

这将显示以下选项卡

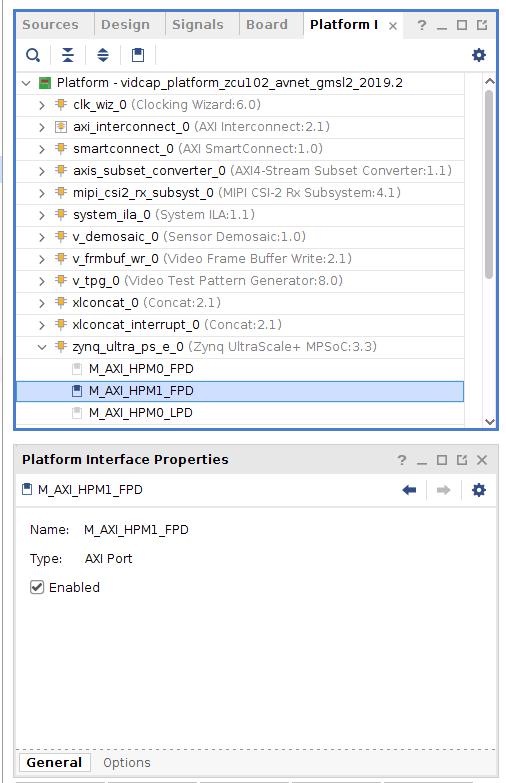

每个选定的接口都有与之相关的属性。下面对修改后的接口属性进行了概述

- clk_wiz_0

- clk_out1

- enabled – true

- id - 0

- is_default – true

- proc_sys_reset - /proc_sys_reset_0

- clk_out2

- enabled – true

- id - 1

- is_default – false

- proc_sys_reset - /proc_sys_reset_1

- clk_out1

- zynq_ultra_ps_e_0

- M_AXI_HPM1_FPD

- enabled – true

- S_AXI_HP1_FPD

- enabled – true

- sptag – HP1

- S_AXI_HP2_FPD

- enabled – true

- sptag – HP2

- S_AXI_HP3_FPD

- enabled – true

- sptag – HP3

- M_AXI_HPM1_FPD

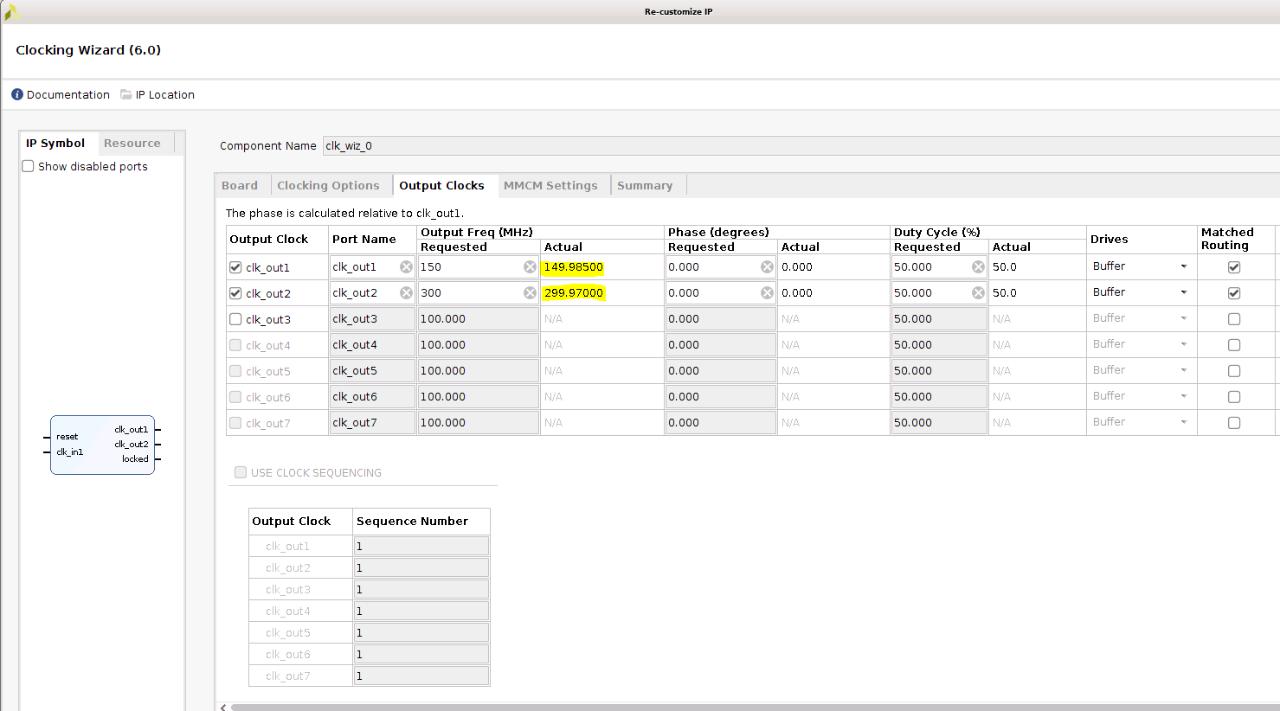

- clk_wiz_0 模块生成将供 DPU 使用的时钟。DPU 有 2 个需要驱动的时钟输入:s_axi_aclk 用于 S_AXI 接口,dpu_2x_clk 用于内部处理逻辑。dpu_2x_clk 频率应是 s_axi_aclk 频率的 2 倍。此设计的时钟向导具有以下配置

N注意输出时钟的“Actual Output Freq (MHz)”设置,因为这些值稍后将在 Vitis 中用于确定 DPU 使用的时钟。

该平台还需要与每个时钟关联的重置,由 proc_sys_reset_1 和proc_sys_reset_0 实现。由于这些时钟/重置仅连接到 DPU(设计中尚不存在),所以它们处于浮动状态。

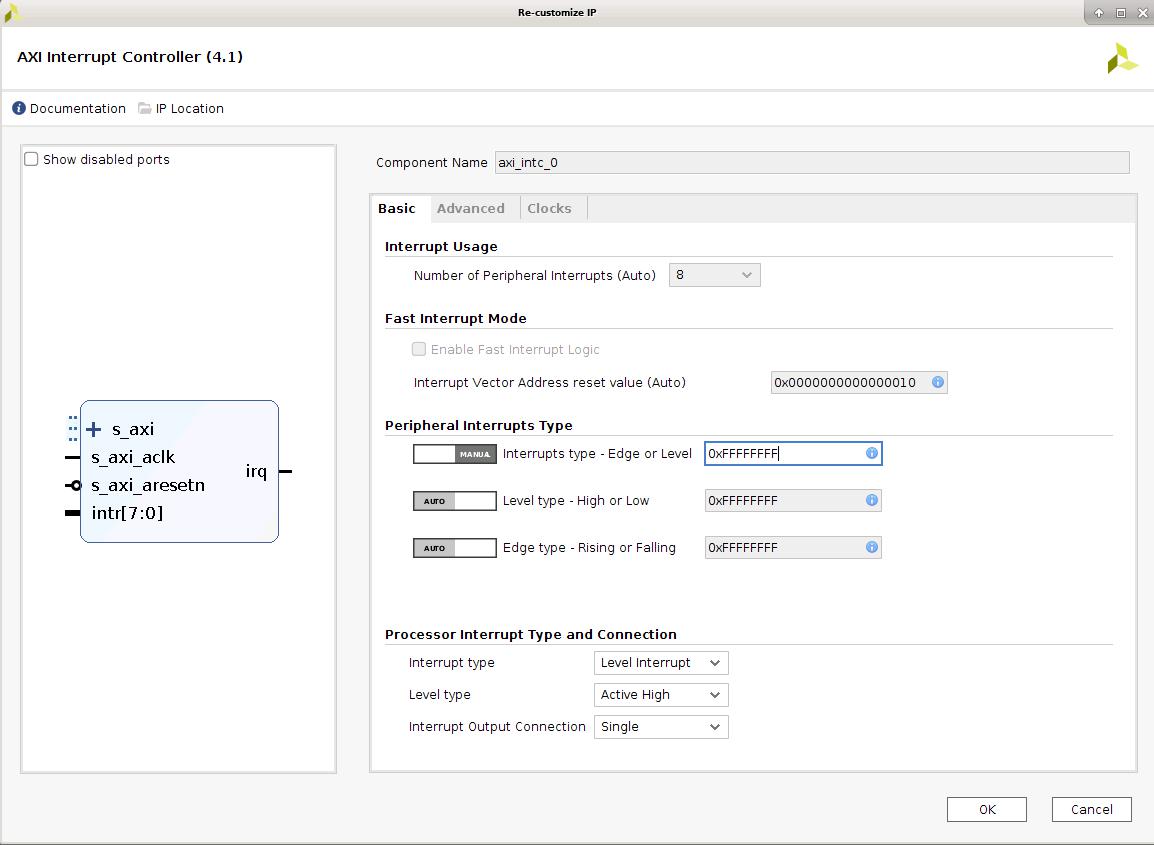

添加axi_intc_0 中断控制器供 DPU 使用。它连接Zynq Ultrascale+ MPSoC pl_ps_irq0 输入并针对电平敏感中断进行配置

axi_intc_0 的内置输入连接配置为 8 个输入的xlconcat_interrupt_0。值得注意的是,所有输入都由 xlconstant_gnd 接地。

如前所述,该设计还附加了一个名为 dynamic_postlink.tcl 的脚本。这是负责断开从 xlconstant_gnd 到 xlconcat_interrupt_0 连接的脚本。该文件现在不执行,而是在 Vitis 链接阶段执行。不过它已经附加到设计中,便于 Vitis 感知。xlconstant_gnd/xlconcat_interrupt_0 和脚本之间的命名约定匹配非常重要。

继续阅读 《Vitis AI 加速 GMSL摄像头人脸检测》第三部分