在嵌入式平台上实现人工智能(AI)

缘由

现场可编程门阵列(FPGA)是一种灵活的硬件结构,从数字信号处理任务到高性能 I/O 再到可靠的安全关键组件,通常是嵌入式系统多个不同方面的必要组成部分。由于 FPGA 拥有强大的并行计算能力,它们也是实现图像处理应用的理想选择。

如今,许多图像分析任务,如目标检测或图像分割等,都是通过神经网络方法实现的。这种方法在准确度上往往显著优于我们所熟知的经典图像处理算法。但是缺陷在于,卷积神经网络(CNN)通常对计算能力、算术运算和数据存储有严格的要求。

由于 FPGA 上的资源有限,因此在 FPGA 上实现神经网络时,极为需要优化的架构和网络设计。为此,改进一般是通过问题驱动和目标驱动战略来实现的。问题驱动优化覆盖模型选择或模型精细化等方面,而目标驱动优化则以最大限度地缩短目标平台上的推断时间为目标。

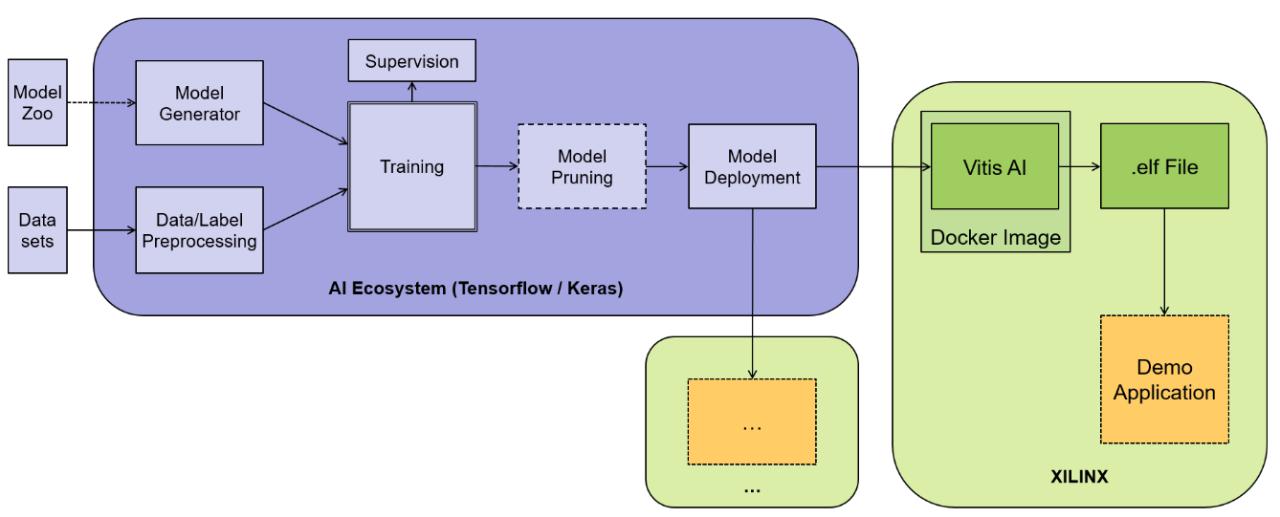

本文总结了 Solectrix 所做的工作,旨在在嵌入式平台上实现人工智能(AI)方法。我们的工作属于 AI 生态系统,因而能够指定和执行从模型生成、训练、模型修剪直至最终模型部署在内的所有所需的步骤。为了让网络推断工作能在赛灵思 FPGA 上运行,必须生成一个中间格式。而且这个中间格式能被针对卷积神经网络的可配置 IP 加速器--赛灵思深度学习处理器单元(DPU)解读并执行。

实验结果证明了被探讨的AI生态系统的功能,以及精心设置的模型形状和开展模型修剪等优化方法的作用。

网络压缩

正如前文所述,神经网络已在计算机视觉和机器智能领域内的许多方面掀起变革,包括分段任务、分类任务和检测任务。通过调整神经网络以求得尽可能高的准确度,让现代 CNN 普遍深度大、复杂而且计算成本高昂。因此,在移动电话或嵌入式器件等资源受限的平台上部署先进的 CNN,是一项极具挑战性的工作。

理论界对压缩神经网络结构和在最终目标器件上为它们加速的各种不同方法进行了大量研讨。

所需的位深度用量化进行限制,不重要的重量或滤波器 [1] 则用修剪方法来发现和移除。此外,Winograd 变换 [2] 或低阶矩阵分解等数学概念可用于实现进一步加速。

然而除了上述方法,对于高效、具备实时能力的网络设计,选择合适的网络结构也起着至关重要的作用。

以下两个章节将简要概述网络类型和结果章节使用的修剪方法。

网络选择

本章节简短描述了我们选择的网络结构。通常来说,最终选择的网络应始终有项目专用性,而且一般由应用和选择的目标平台共同组成。如欲了解更详细的讨论和不同网络类型的概述,读者敬请参阅引用的文献 [3-11]。

就我们在结果章节中讨论的应用,我们选择 MobileNetV2 结构作为基本网络类型。

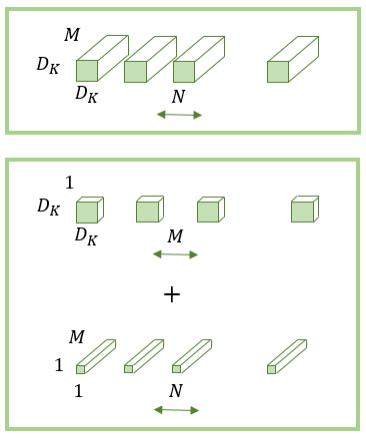

MobileNets 首次发布于 2017 年 [7],旨在让神经网络适用于移动设备或嵌入式目标设备。该架构基于深度可分卷积,以构建轻量化深度神经网络。深度可分卷积的概念如图 1 的中图和下图所示。标准卷积则如图 1 中上图所示。正如图中所示,深度可分卷积由深度卷积和逐点卷积共同构成。现在对于给定的大小为 DFxDF 的特征图,内核大小是 DKxDK,输入通道数是 M,输出通道数是 N,常规卷积的计算成本是 DF·K·DF·D·DF·D·c·K·D·K·K。相比之下,深度卷积的成本是 DF·DF·DK·DK·M,加上逐点卷积,深度可分卷积的总成本可以写作:DF·DF·DK·DK·M+DF·DF·M·N。正如 [7] 中所论述的,MobileNets 使用 3x3 深度卷积滤波器,仅略微牺牲准确度,计算成本就比标准卷积降低 8 到 9 倍。

此外,在 2019 年发布的 MobileNetV2 [8] 基于翻转残差结构,在保持准确度的同时,进一步显著降低了所需的运算数。本文提出一种新颖的层类型,称为有线性瓶颈的翻转残差。在输入端,该模块采用低维度压缩表达。这种表达先被展开成较高维度,然后用轻量化深度卷积进行过滤。接着用线性卷积将获得的特性投影回低维度表达。

网络修剪

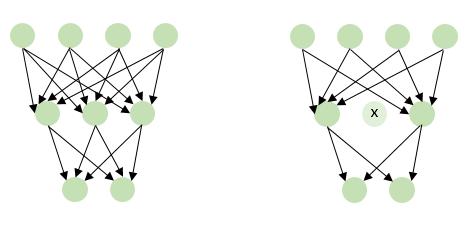

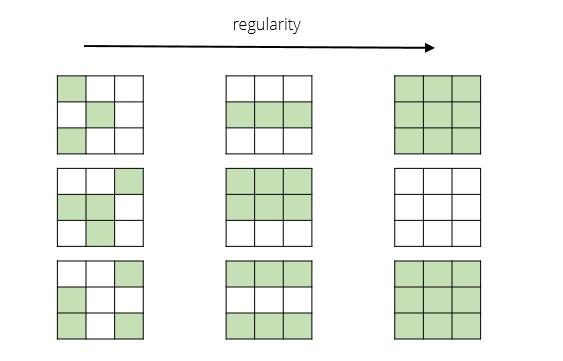

本章节简要概述选择的修剪方法 [12]。正如前文所提及的,网络修剪可以进一步压缩神经网络。一般情况下,这是通过搜索、发现和删除不重要的权重或完整的特性通道来实现的。之后,修剪后的模型再经过数次重新训练,以补偿修剪步骤导致的准确度下降。

在权重修剪中,删除个别权重或将其设置成零。作为简单的标准,最小的绝对权重可能被选中。不过文献里也提议过许多其他的方法。作为对比,在通道修剪中,删除完整的通道。判断应删除的通道的简单标准是绝对通道权重的最小总和。

文献中可以找到用于权重修剪、通道修剪、硬修剪或软修剪的不同示例 [12-16]。

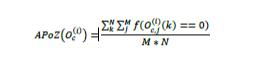

在 [12],我们为后续讨论的试验结果选择的方法中,零激活的平均百分比(APoZ)被提议作为修剪标准。根据 [12],APoZ 的定义是在 ReLU 映射后,衡量神经元的零激活的百分比,因此位于激活层后。为此,令 Oc(i) 代表第 i 层第 c 通道的输出。其 APoZ 值可写作:

其中如果为假,f(·)=0。如果为真,f(·)=1。此外,???? 代表输出特征图的维度,???? 代表为测量激活数量而使用的测试样本数。

因此可以看出,APoZ 标准简单地计算激活后神经元或滤波器为零的频次。因为该值被输出大小和样本数均一化,可以使用 0 到 1 间的简单阈值来控制修剪过程。请注意:选择较高的阈值会减少移除的权重数或滤波器数。

需要注意的是,具体修剪方法的选择始终取决于最终目标平台或给定的项目要求。因此对于优化用于嵌入式系统的 AI 应用而言,完全地控制网络修剪过程是一项必不可少的环节。

AI 生态系统

本章节讨论我们的 AI 生态系统,介绍从模型生成、训练、网络修剪到模型部署,覆盖所有步骤的完整框架。在下一章节,以赛灵思 MPSoC为例,展示如何最终部署到所需的目标平台上。

尽管有许多潜在的深度学习框架,作为起步我们决定重点关注未来前景可能最好的 Tensorflow/Keras。生态系统围绕实际框架构建,通过定制层、模型、可重复使用的功能和工具,提供功能扩展。它随着新用例和新应用的涌现而发展,在模型生成、数据集编译、训练、可选修剪和最终模型部署方面,始终提供标准的工作流程。

图 4 所示的是我们 AI 生态系统的工作流程基本概念。我们将在后续的小节里对其进行更详细的探讨。

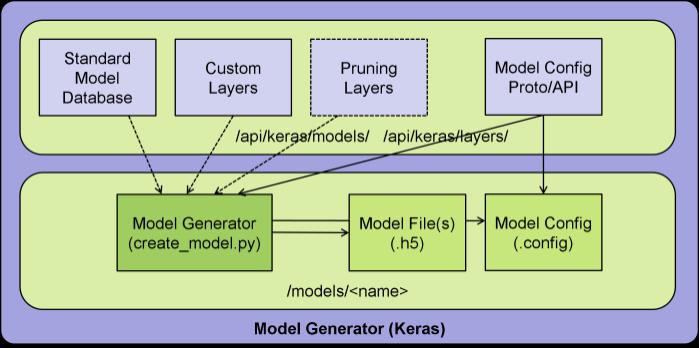

模型生成器

就模型生成而言,可从数据库选择模型。这通常包括文献中提议的知名模型。或者,也可以定义完整定制的模型。为将模型适配到实际的目标应用,可以从生态系统的层命名空间使用定制层。这种做法也可用于修剪目的,例如 AutoPruner 方法就要求这样做 [16]。为方便配置,使用谷歌中间格式 protobuf。使用 python 脚本 create_model.py,即可创建模型文件,含网络拓扑及其参数化。进一步的辅助信息用模型配置文件来表达。取决于模型生成,得到的 h5 文件也许已经包含预训练的权重。

模型生成如图 5 所示。

数据集编译器

除了上个小节里讨论的总体网络结构,使用的数据集也可以配置。对此,可以选择有相应的注释数据的所需数据库。数据集可以使用自己的图像数据单独设计,也可以与公开提供的数据相结合。在 python 脚本 create_dataset.py 中,数据集可以细分成训练集和验证集。最后,创建结果分别是描述重要辅助信息的配置文件和 pkl 或 h5 格式的数据容器。尽管 pkl 格式只提供图像路径,h5 格式直接包含图像数据。因此,容器格式有明确的大小区别,可根据具体的训练环境进行选择。

数据集配置如图 6 所示。

训练

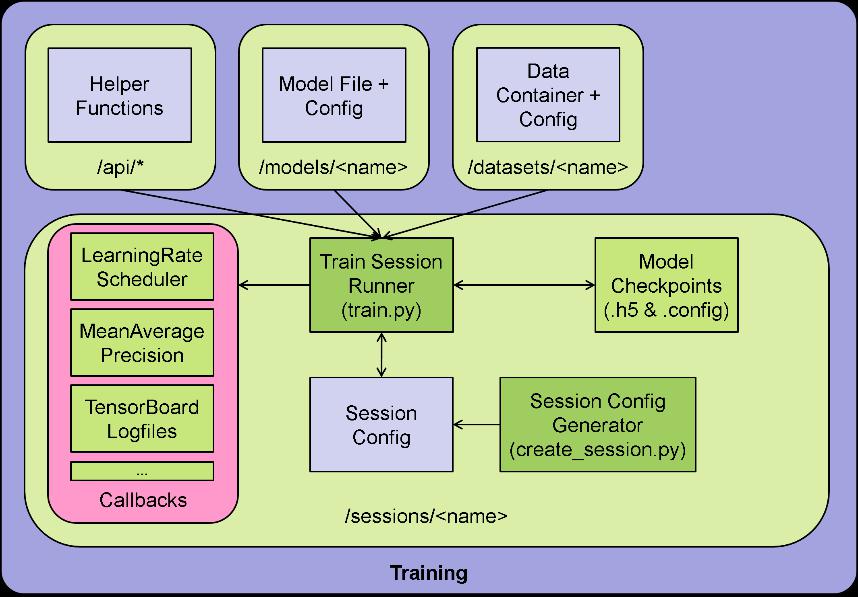

要初始化训练,可以用脚本 create_session.py 创建一个内含模型和数据集的会话。会话包含设定模型训练条件的训练专用设置,如学习率调度器参数、批处理大小、训练次数等等。

训练本身用 python 脚本 train.py 控制。可以激活各种 Keras 回调,例如用于适配学习率、计算当作准确度指标的平均精确度或是获取不同的 tensorboard 日志文件等用途。训练流程在每次训练后存储模型检查点,以便之后继续训练流程。

模型训练如图 7 所示。

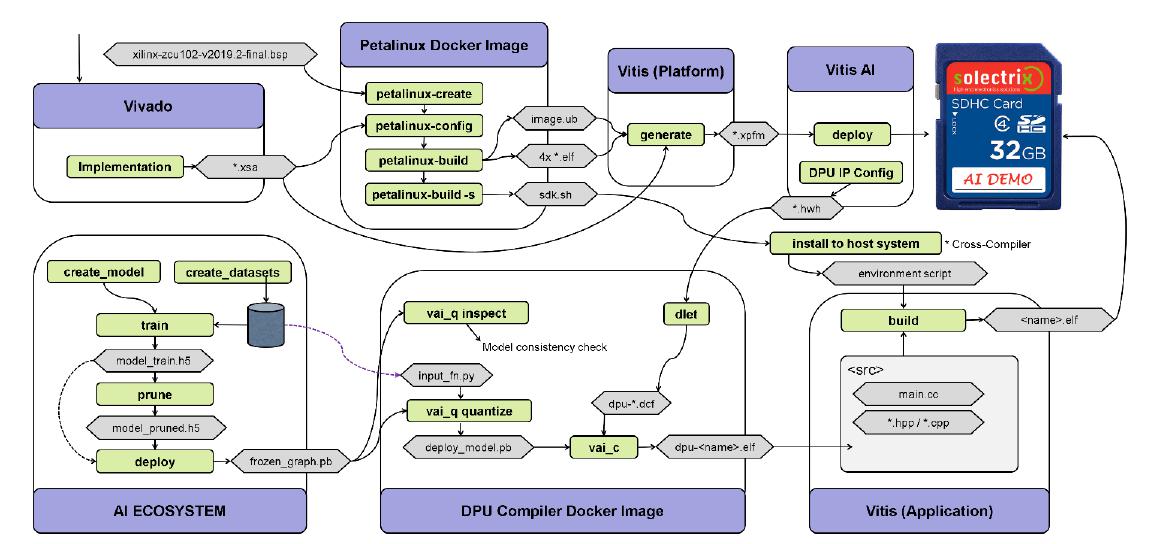

赛灵思 ZCU102 评估套件工作流程

在完成对 Solectrix 内部 AI 生态系统背后的主要构思的讨论后,本章节介绍集成 AI 生态系统和在边缘器件上实现网络推断的基本工作流程。用作模型示例的目标硬件,选择了赛灵思 ZCU102 评估套件,因为它采用强大的赛灵思 MPSoC 器件,能包含多个 DPU 核心。该工作流程如图 8 所示,并在下文中略加讨论。

如之前的章节里介绍的,网络训练要求基本模型结构与适当的训练数据相结合。在 AI 生态系统内,受训网络被表达成 hdf5(.h5)文件。网络经训练和有选择的修剪后被部署,意即一切都只是训练需要,但不是后续网络推断需要的元素都被移除。部署结果是一个 Tensorflow 冻结图形模型。接下来,冻结图形被馈入 Vitis AI(VAI)Tensorflow 转换工具。通过用检查命令 vai_q_tensorflow 检查,可以验证网络的拓扑,确保所有算符都受赛灵思 DPU 核心支持。然后量化网络,使之能用 8 位数据表达。量化需要另一个数据集。这个数据集被 VAI 量化器工具 vai_q_tensorflow quantize 用于优化量化参数。

深度学习处理器单元(DPU)的 IP 核心用赛灵思 Vivado 或 Vitis 配置并实现在 FPGA 图像中,具体取决于所选择的工作流程。然后 Vivado/Vitis 生成的硬件交接文件(hwh)被馈送给 VAI。工具 dlet 被用于从 hwh 文件提取 DPU 配置参数。最后为了进行编译,使用 Vitis AI Compiler vai_c_tensorflow,以转换 Tensorflow 网络格式为二进制 blob 文件,供 DPU 执行。

完成网络结构编译后,所需的应用就能实现在 Vitis 中,编译后的网络被集成到应用中。

以 PetaLinux 为操作系统,用其生成的 sdk.sh 主机编译器环境工具,应用最终为目标硬件完成交叉编译。请注意具体的 PetaLinux 配置并不属于本文篇幅范围。

试验结果

本章节展示部分试验结果并确认上文讨论的工作流程的基本原理。

模型训练

用作一个可以运行的例子,我们决定创建一个完全定制的 MobileNetV2 SSD(单插槽多框检测器)[17],用于识别我们 Solectrix 的公司标识,无论其方向、比例尺和背景如何。作为图例,图 9 展示的是一个示例图像。该模型使用超大 1024x1024x3 像素输入图像,以便在 6 个分辨率比率上进行高分辨率检测。我们包含了 12 个 MobileNetV2 块,每层的最大深度是 512 个滤波器。推断模型包括整个特征提取器基干和 SSD 检测器使用的卷积层。SSD 框结果后续在嵌入式 ARM CPU 中进行解码。

使用的数据集由 503 幅图像构成。在这些图像中,可检测的标识数量在 1 到 40 间变化。为评估目的,数据集被划分成训练数据(约95%)和验证数据(约 5%)。显然,图像数量对于真正的项目驱动应用而言太少。但是该数据集对用作示范目的的工作流程示例是足够适合的。

最初,设计的模型由 880,124 个参数构成。

为了强化数据,使用下列的光度失真、随机裁剪、随机缩放、随机翻转和随机框展开等运算。

该模型被训练 120 次,每次 1,000 个迭代。在训练过程中,学习率在 0.001 到 0.03 范围中进行调整。训练损耗和验证损耗到达收敛状态,训练数据集的最终平均精确度达到 0.9,验证数据集的最终平均精确度达到 0.98。

模型修剪

在完成模型训练后,技术上已为部署做好准备。执行可选的修剪步骤的目的是展现减少参数对检测性能的影响。对修剪方法选择了上文提及的 APoZ 标准 [12]。

基本策略是调整 APoZ 阈值,移除卷积层最不活跃的滤波器。因为必须对整个训练数据集开展全网络的活动特征分析,用微小的德尔塔循环修剪小 ConvD 层的群组是有利的做法。每次循环后需要使用精细的调整步骤,让模型调整剩余滤波器,补偿移除的滤波器。由于每次循环后对模型的影响相对较小,这一般只需几次训练迭代。每次迭代后使用平均精确度指标验证模型。这便于监督修剪进展并实现决策,决定选择哪个修剪阶段用于部署。

在我们的示例中,多次迭代的 APoZ 阈值在 0.9 到 0.25 之间变化。相关的 Conv2D 层被识别出来并划分成 9 个层组。此外,修剪工具将剩余滤波器的数量限定为 4 的乘数,目的是让推断目标架构高效地运用并行 DPU 乘法器资源。这只是将目标推断平台包含在优化策略范围内的一个方面。

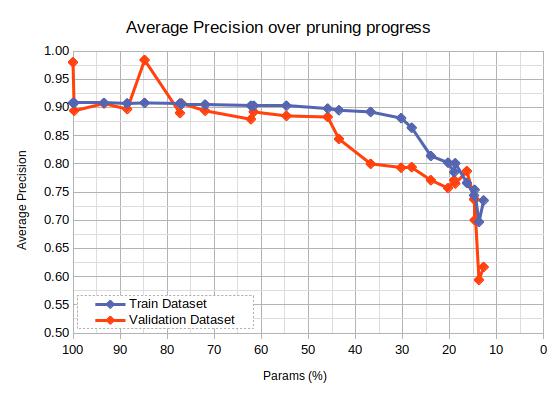

图 10 所示的是修剪过程中减少参数后的性能与模型平均精确度的比较。因为我们案例中的验证数据集非常小,它不能准确地反映所需应用的整体性能。因此我们也使用训练数据集,用比较来衡量模型的准确性。取得的进展发现可行的做法。移除的卷积滤波器越多,模型就越小。图中每个点都代表一个被保存的经修剪的模型。

对于最终部署,我们选择的是一个已经缩小到 404,052 个参数的模型,大致是原始模型的 45.9%,但平均精确度接近原始模型(训练集:0.898,验证集:0.883)。更进一步缩小会造成严重不可接受的准确度降低。

整个迭代修剪过程仅使用与模型训练本身相同的时间,因此它是一种十分重要的优化工具。

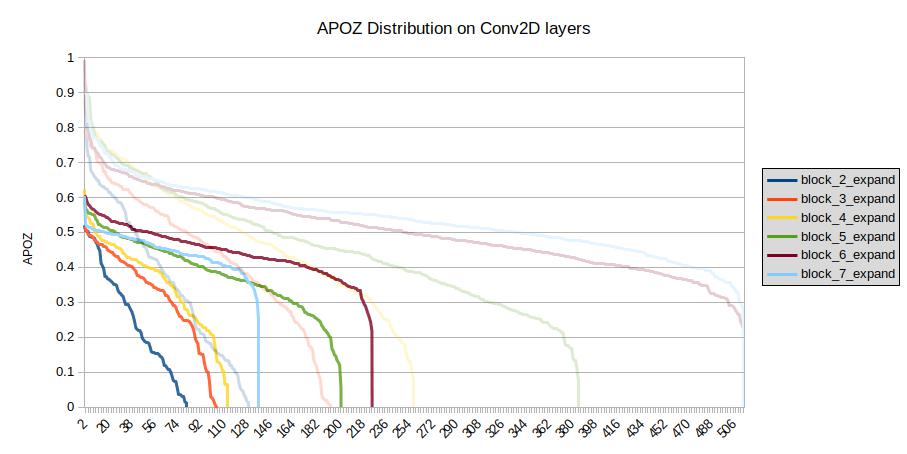

图 11 所示的是受训模型和修剪模型的选定 Conv2D 层的 APoZ 值的分布(活动特征分析)。ApoZ 值用 y 轴显示,滤波器数量则用 x 轴显示。根据图例的描述,不同的 Conv2D 层用不同的颜色显示。正如前文所提到的,每层的滤波器数量限制在 512 个,对应于其在 x 轴上的最大值。每层的值按降序进行排序。APoZ 值 0 对应于 100% 激活,APoZ 值接近 1 对应于滤波器极少激活,因此对模型的最终输出基本没有关联。

比较两个模型,可以观察到两种效应。首先,经过修剪后滤波器的数量有一定程度的下降。这是修剪的真实目的。修剪后每层最大滤波器数量是 224 个,修剪前某些层的滤波器数量是 512 个。其次,最大 APoZ 值也有所下降。这说明总体活性度有所增加。

受训模型和经修剪模型的第二个比较见下图 12。该图所示的是用受训网络和经修剪网络在 ZCU201 评估板上分别运行推断示例的情况。正如该图所示,两个网络都能令人信服地在测试图像中以不同比例尺和角度,检测出这幅来自我们网站的示例图像里的四个 Solectrix 公司标识。所有检测都用其对应的边界框进行标注。此外还给出了网络置信度。可以看到,检测框的置信度和位置有一定程度的变化。但是,尽管模型尺寸大幅缩小,它仍然检测出所有四个 Solectrix 标识。

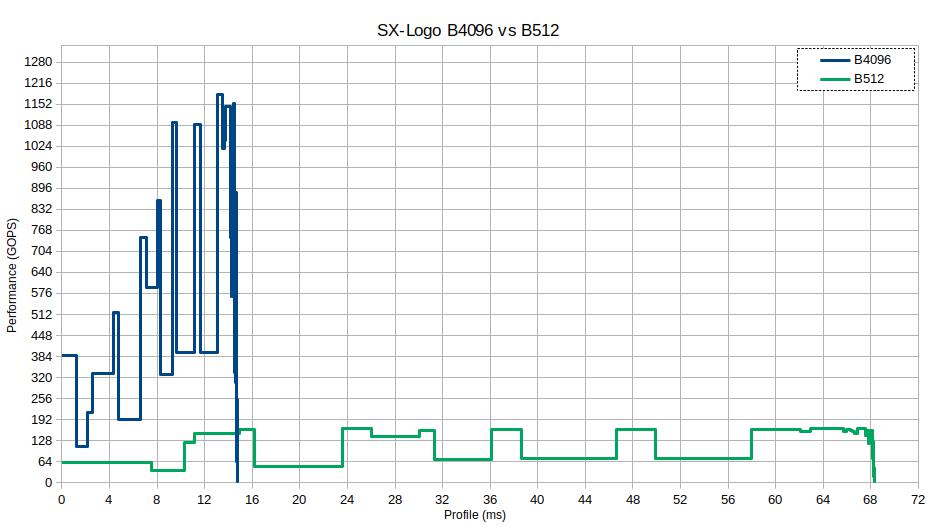

最终,在最后一个实验中,评估被使用的 DPU 核心的负载。为此目的使用了两种不同的配置。第一种配置是每时钟周期 512 次运算,第二种配置是每时钟周期最高 4,096 次运算。下文中这两种配置分别用 B512 和 B4096 指代。在使用 325MHz 的 DPU 时钟时,B512 和 B4096 的最高性能分别是 166.4 GOP/秒和 1331.2 GOP/秒。

接下来使用 DPU 核心的特征分析模式,测量了推断用时。图 1 比较了两种被研究的 DPU 配置的性能和运行时间。B512 的性能用绿色显示,B4096 的性能用蓝色显示。可以看出,B512 的总推断时间大约是 68 ms。作为对比,B4096 的推断时间大约是 15 ms。因此两种配置间的运行时间差异比大约是 4.5,显然不同于理论最优比 8.0。另外还可以观察到性能并不恒定,会随不同的网络层发生改变。

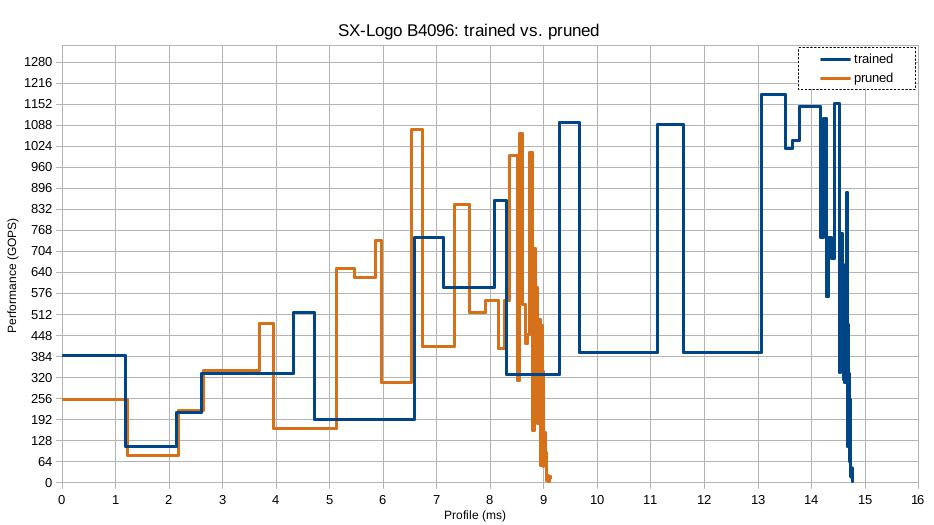

图 14 是 B4096 DPU 配置下受训模型和经修剪模型间的性能比较。受训模型仍以蓝色显示,经修剪模型用橙色显示。在该图中可以观察到两个有趣的现象。首先,经修剪模型的推断时间比未经修剪、只受训练的模型要短大约 5.5 ms。这相当于推断时间缩短约 38.4%。而且它也显著不同于在经修剪模型上观察到的 54.1% 的参数减少。因此,参数的数量下降并不会自动地引起目标硬件上同等幅度的推断时间下降。其次,对于某些层,尤其是早期网络层,修剪可以显著地降低参数数量,但不会显著地缩短推断时间。因此对于这些层,只要参数数量不属于主要的优化标准,将它们从修剪中排除以从最大滤波器深度获益,是一种极为有益的做法。

因此,在模型训练前对不同设计的网络的推断时间开展特征分析,可能有一定助益。通过这样做,就可以找出在配置后的 DPU 核心结构上提供接近最优性能的模型。

总结与展望

本文是对 Solectrix 为在嵌入式平台上实现人工智能(AI)方法所做的工作的总结。本文先讲解部分基本网络模型和修剪方法,继而讨论公司的内部工具“Solectrix AI 生态系统”。接着简单介绍在 ZCU102 评估板上使用受训网络的工作流程。最后,通过试验结果强调 DPU配置和修剪对目标硬件上的最终推断时间的影响。

如图 11 所示,在体现第一个 Conv2D 层上的实际 DPU 性能的第一个间隔里,修剪的效果完全未能缩短推断的时间。这可能是技术约束造成的,如带宽限制或赛灵思 DPU 核心的并行化属性。尽管模型优化的重点是改善时延,降低深度不能提供助益。层的深度甚至可以在不对推断时间造成任何影响的情况下加大。其他层可以在修剪后努力增加使用 DPU,从而改善 DPU 计算资源的利用率,缩短处理时间。

Solectrix 目前正在系统地研究应如何参数化 CNN 运算,以实现尽可能大的 DPU 使用率。这个目标驱动的优化策略将包括赛灵思 DPU 属性的相关知识或是任何其他嵌入式目标平台的相关知识,以尽可能最大限度地利用计算能力。我们的修剪策略将优化一个模型,为底层架构找到最佳的优化点。

根据我们的研究结果,我们坚定地认为,修剪应构成嵌入式 AI 应用开发过程中的必备步骤。

如欲了解更多信息,敬请访问 www.solectrix.de

参考资料

[1] S. Han, H. Mao, W. Dally, „Deep Compression: Compressing Deep Neural Networks with Pruning, Trained Quantization and Huffman Coding“, 2016

[2] L. Meng, J. Brothers, “Efficient Winograd Convolution via Integer Arithmetic”, 2019

[3] K. Simonyan and A. Zisserman, „Very Deep Convolutional Networks for Large-Scale Image Recognition“, 2015

[4] K. He, X. Zhang, S. Ren, J. Sun, “Deep Residual Learning for Image Recognition”, 2015

[5] F.N. Iandola, S. Han, M., Moskewicz, K. Ashraf, W. J. Dally, K., Keutzer, “AlexNet-Level Accuracy with 50x Fewer Parameters and <0.5MB Model Size”, 2017

[6] X. Zhang, X. Zhou, M. Lin, J. Sun, “ShuffleNet: An Extremely Efficient Convolutional Neural Network for Mobile Devices”, 2017

[7] A. G. Howard, M. Zhu, B. Chen, D. Kalenichenko, W. Wang, T. Weyand, M. Andreetto, H. Adam, “MobileNets: Efficient Convolutional Neural Networks forMobile Vision Applications”, 2017

[8] M. Sandler, A. Howard, M. Zhu, A. Zhmoginov, L.-C. Chen, “MobileNetV2: Inverted Residuals and Linear Bottlenecks”, 2019

[9] M. Tan, B. Chen, R. Pang, V. Vasudevan, M. Sandler, A. Howard, Q.V. Le, „MnasNet: Platform-Aware Neural Architecture Search for Mobile“, 2019

[10] A. Howard, M. Sandler, G. Chu, L.-C. Chen, B. Chen, M. tan, W. Wang, Y. Zhu, R. Pang, V. Vasudevan, Q. V. Le, H. Adam, “Searching for MobileNetV3”, 2019

[11] T. Yang, A. Howard, B. Chen, X. Zhang, A. Go, M. Sandler, V. Sze, H. Adam, “Netadapt: Platform-aware neural network adaptation for mobile applications”, 2018

[12] H. Hu, R. Peng, Y.W. Tai, C.K. Tang, “Network Trimming: A Data-Driven Neuron Pruning Approach towards Efficient Deep Architectures”, 2016

[13] H. Mao, S. Han, J. Pool, W. Li, X. Liu, Y. Wang, W. Dally, “Exploring the regularity of sparse structure in convolutional neural networks”, 2017

[14] J.H. Luo, H. Zhang, H.Y. Zhuo, C.W. Xie, J. Wu, W. Lin, “ThiNet: Pruning CNN Filters for a thinner net”, 2018

[15] Y. He, G. Kang, X. Dong, Y. Fu, Y. Yang, “Soft Filter Pruning for Accelerating Deep Convolutional Neural Networks”, 2018

[16] J.H. Luo, J. Wu, “AutoPruner: An End-to-End Trainable Filter Pruning Method for Efficient Deep Model Inference”, 2019

[17] W. Liu, D. Anguelov, D. Erhan, C. Szegedy, S. Reed, C.-Y. Fu, A. Berg, “SSD: Single Shot MultiBox Detector”, 2016